# **M.Sc. PHYSICS - I YEAR**

# **DKP13 : DIGITAL ELECTRONICS**

# SYLLABUS

# UNIT I Number systems

Binary coded decimal number system, Grey code, Grey code to Binary conversion, Binary to Grey code, Excess 3 code, Decimal to excess 3 code, ASCII code.

Universal logic gates: NAND and NOR gates as universal logic gates – Simplification of logic circuits – De Morgan's laws – Boolean laws – Karnaugh maps – three variable and four variable maps – max and min terms.

# **UNIT II Arithematic circuits**

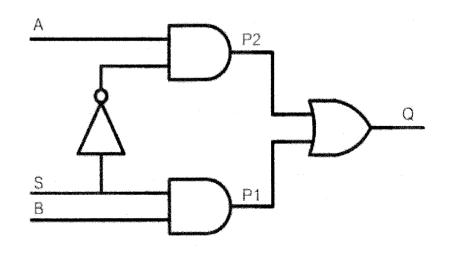

Half adder – Truth table and circuit – Full adder – Truth table and circuit – Four bit adder – Half subtractor – Full subtractor – <u>Multiplexer</u>: Four input multiplexer – Applications of Multiplexer – demultiplexer – Decoders 2 to 4 decoder – BCD to seven segment decoder – encoders.

# **UNIT III Flipflops**

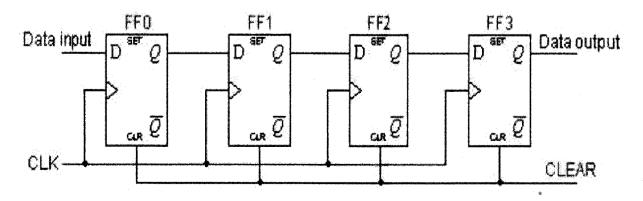

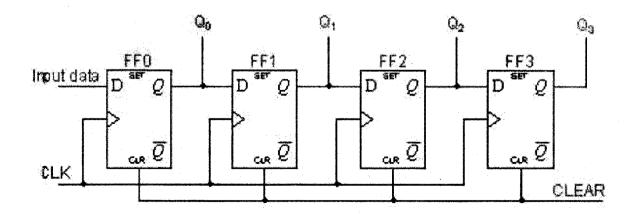

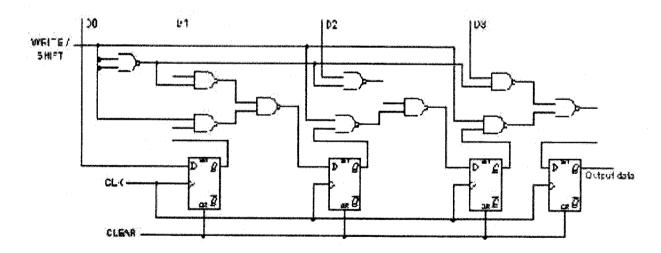

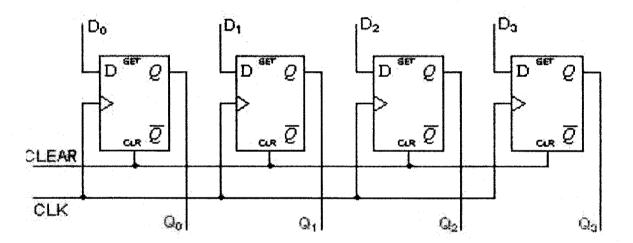

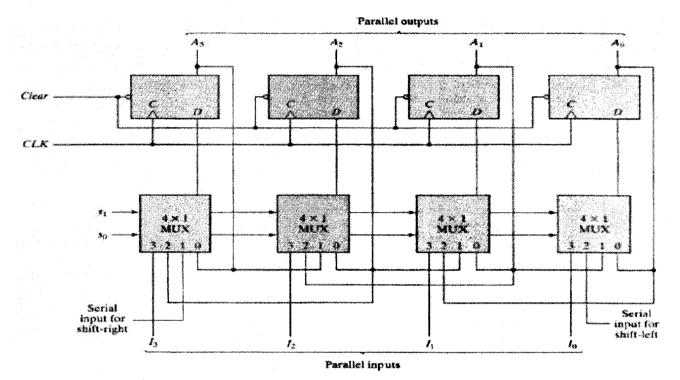

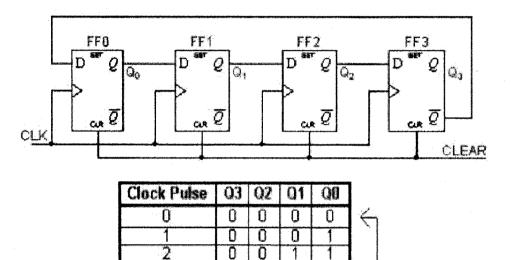

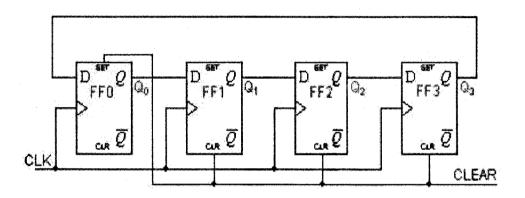

Introduction – NAND LATCH, J K flipflop – J K Master – slave flipflop – D flipflop and T flipflop – <u>Registers and Counters</u>: Shift registers – serial in – parallelout, serial in – serial out, parallel in – serial out, parallel in – parallel out shift registers – wave forms for the above – Counters – up counters, down counters, decade counters, timing sequences, Mod – n counters.

# UNIT IV MULTIVIBRATORS

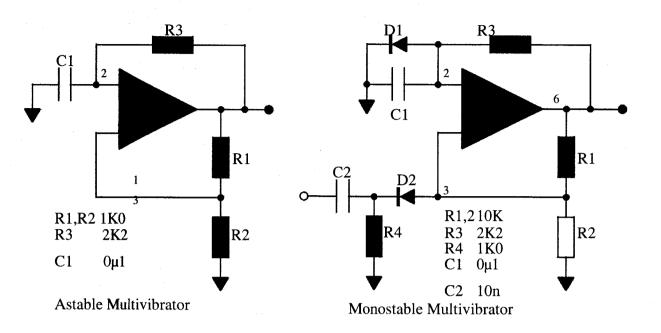

Classification of multivibrators – Astable, monostable, bistable multivibrators using operational amplifier.

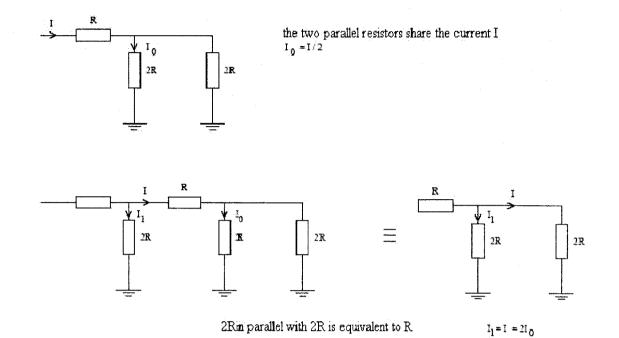

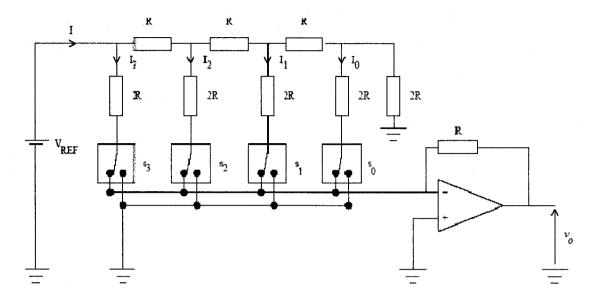

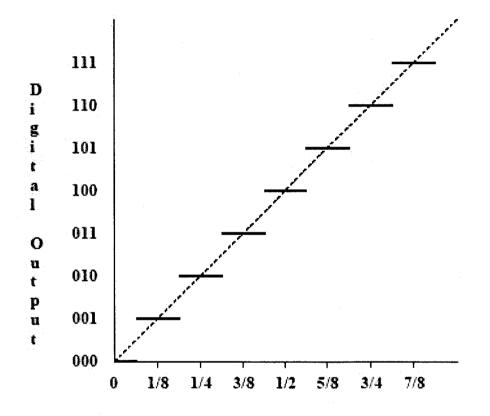

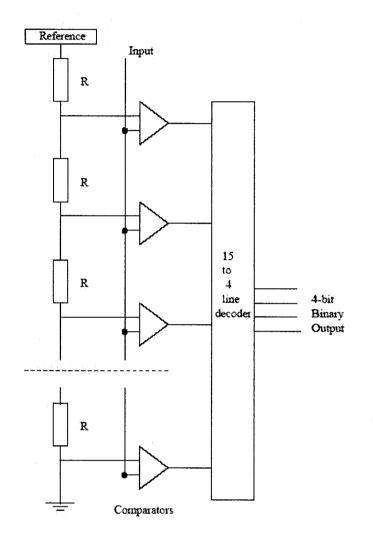

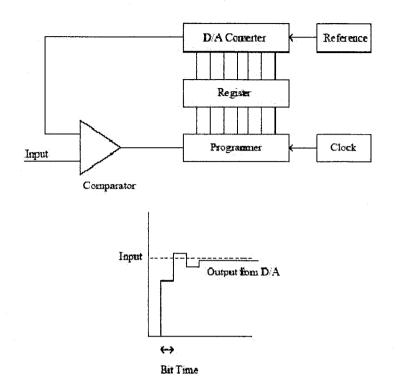

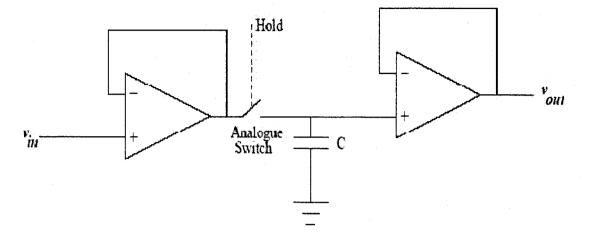

<u>D/A and A/D converters</u>: Binary weighted register D/A converter using Op-Amp - R-2R ladder D/A converter with Op-Amp - Analog to Digital converters (ADC) - their characteristics.

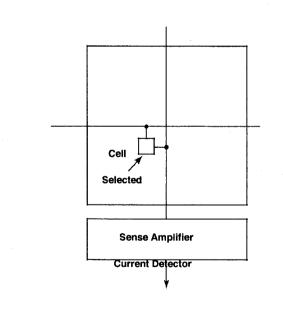

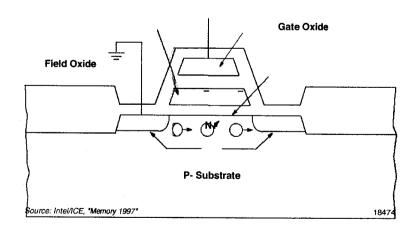

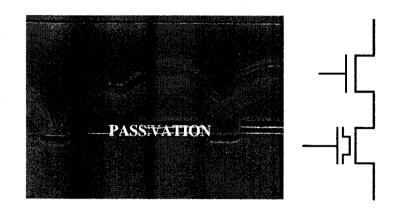

# UNIT V SEMICONDUCTOR MEMORIES

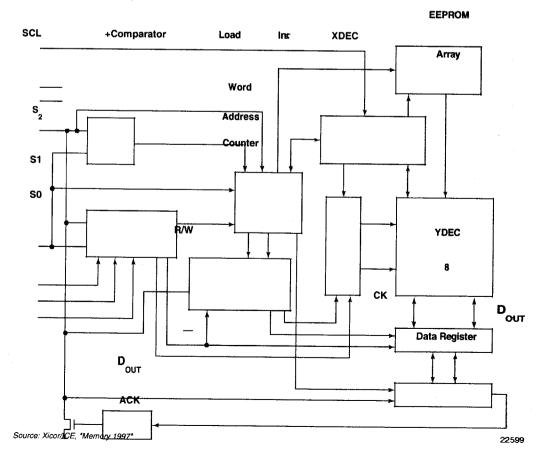

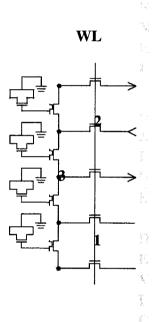

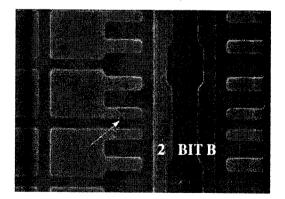

Memory cell unit – ROM, RAM – Their classifications – ROM, PROM, EPROM, EEPROM, RAM, Static RAM, dynamic RAM, Memory read and memory write operations – Flash memory - Charge coupled Device (CCD).

# **Books for Study and Reference:**

1. Digital Electronics principles and applications – Soumitra Kumar Mandal - Tata MCGraw Hill publications – New Delhi.

2.Integrated Electronics – Digital and Analog – V.Vijayendran (S.Viswanathan printers and publications ) - 2005

3.Digital Electronics by Millman and Taub

4. Electronics Fundamentals and Applications- John D Ryder

Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli.

# MS UNIVERSITY M.Sc., Physics Correspondence Course

# Paper Title : DIGITAL ELECTRONICS

UNIT 1 NUMBER SYSTEM Binary coded decimal number system, Grey code, Grey code to Binary conversion, Binary to Grey code, Excess 3 code, Decimal to excess 3 code, ASCII code. Universal logic gates: NAND and NOR gates as universal logic gates – Simplification of logic circuits – De Morgan<sup>®</sup>s laws – Boolean laws – Karnaugh maps – three variable and four variable maps – max and min terms.

#### Binary Coded number system

Binary codes are codes which are represented in binary system with modification from the original ones. There are two types of binary codes: Weighted codes and Non-Weighted codes. BCD and the 2421 code are examples of weighted codes. In a weighted code, each bit position is assigned a weighting factor in such a way that each digit can be evaluated by adding the weight of all the 1's in the coded combination.

Weighted Binary Systems

#### ✓ 8421 code/BCD code

The BCD (Binary Coded Decimal) is a straight assignment of the binary equivalent. It is possible to assign weights to the binary bits according to their positions. The weights in the BCD code are 8,4,2,1.

**Example:** The bit assignment 1001, can be seen by its weights to represent the decimal 9 because 1x8+0x4+0x2+1x1 = 9

#### Weighted Code

– 8421 code

- Most common

- Default

• The corresponding decimal digit is determined by adding the weights associated with the 1s in the code group.

$-62310 = 0110\ 0010\ 0011$

- 2421, 5421,7536, etc... codes

• The weights associated with the bits in each code group are given by the name of the code

#### **Nonweighted Codes**

#### **–** 2-out-of-5

Non Weighted codes are codes that are not positionally weighted. That is, each position within the binary number is not assigned a fixed value.

• Actually weighted 74210 except for the digit 0

• Used by the post office for scanning bar codes for zip codes

• Has error detection properties

#### ✓ 2421 code

This is a weighted code; its weights are 2, 4, 2 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 2 + 4 + 2 + 1 = 9. Hence the 2421 code represents the decimal numbers from 0 to 9.

#### ✓ 5211 code

This is a weighted code; its weights are 5, 2, 1 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 5 + 2 + 1 + 1 = 9. Hence the 5211 code represents the decimal numbers from 0 to 9.

#### ✓ **Reflective code**

A code is said to be reflective when code for 9 is complement for the code for 0, and so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, and excess-3 are reflective, whereas the 8421 code is not.

#### ✓ Sequential code

A code is said to be sequential when two subsequent codes, seen as numbers in binary representation, differ by one. This greatly aids mathematical manipulation of data. The 8421 and Excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

#### ✓ Excess-3 code

Excess-3 is a non weighted code used to express decimal numbers. The code derives its name from the fact that each binary code is the corresponding 8421 code plus 0011(3).

**Example:** 1000 of 8421 = 1011 in Excess-3

#### ✓ Gray code

The gray code belongs to a class of codes called minimum change codes, in which only one bit in the code changes when moving from one code to the next. The Gray code is non-weighted code, as the position of bit does not contain any weight. In digital Gray code has got a special place.

| Decimal<br>Number | Binary Code | Gray Code |

|-------------------|-------------|-----------|

| 0                 | 0000        | 0000      |

| 1                 | 0001        | 0001      |

| 2                 | 0010        | 0011      |

| 3                 | 0011        | 0010      |

| 4                 | 0100        | 0110      |

| 5                 | 0101        | 0111      |

| 6                 | 0110        | 0101      |

| 7                 | 0111        | 0100      |

| 8                 | 1000        | 1100      |

| 9                 | 1001        | 1101      |

| 10                | 1010        | 1111      |

| 11                | 1011        | 1110      |

| 12 | 1100 | 1010 |

|----|------|------|

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

The gray code is a reflective digital code which has the special property that any two subsequent numbers codes differ by only one bit. This is also called a unit-distance code.

Important when an analog quantity must be converted to a digital representation. Only one bit changes between two successive integers which are being coded.

## ✓ Error Detecting and Correction Codes

#### • Error detecting codes

When data is transmitted from one point to another, like in wireless transmission, or it is just stored, like in hard disks and memories, there are chances that data may get corrupted. To detect these data errors, we use special codes, which are error detection codes.

#### • Error correcting code

Error-correcting codes not only detect errors, but also correct them. This is used normally in Satellite communication, where turn-around delay is very high as is the probability of data getting corrupt.

#### • Hamming codes

Hamming code adds a minimum number of bits to the data transmitted in a noisy channel, to be able to correct every possible one-bit error. It can detect (not correct) two-bit errors and cannot distinguish between 1-bit and 2-bits inconsistencies. It can't - in general - detect 3(or more)-bits errors.

#### • Parity codes

A parity bit is an extra bit included with a message to make the total number of 1's either even or odd. In parity codes, every data byte, or nibble (according to how user wants to use it) is checked if they have even number of ones or even number of zeros. Based on this information an additional bit is appended to the original data. Thus if we consider 8-bit data, adding the parity bit will make it 9 bit long. At the receiver side, once again parity is calculated and matched with the received parity (bit 9), and if they match, data is ok, otherwise data is corrupt.

#### Two types of parity

-Even parity: Checks if there is an even number of ones; if so, parity bit is zero. When the number of one's is odd then parity bit is set to 1.

-Odd Parity: Checks if there is an odd number of ones; if so, parity bit is zero. When the number of one's is even then parity bit is set to 1.

#### ✓ Alphanumeric codes

The binary codes that can be used to represent all the letters of the alphabet, numbers and mathematical symbols, punctuation marks, are known as alphanumeric codes or character codes. These codes enable us to interface the input-output devices like the keyboard, printers, video displays with the computer.

#### • ASCII codes

Codes to handle alphabetic and numeric information, special symbols, punctuation marks, and control characters.

• ASCII (American Standard Code for Information Interchange) is the best known.

• Unicode – a 16-bit coding system provides for foreign languages, mathematical symbols, geometrical shapes, dingbats, etc. It has become a world standard alphanumeric code for microcomputers and

computers. It is a 7-bit code representing  $2^7 = 128$  different characters. These characters represent 26 upper case letters (A to Z), 26 lowercase letters (a to z), 10 numbers (0 to 9), 33 special characters and symbols and 33 control characters.

#### • EBCDIC codes

EBCDIC stands for Extended Binary Coded Decimal Interchange. It is mainly used with large computer systems like mainframes. EBCDIC is an 8-bit code and thus accommodates up to 256 characters. An EBCDIC code is divided into two portions: 4 zone bits (on the left) and 4 numeric bits (on the right).

#### Example 1: Give the binary, BCD, Excess-3, gray code representations of numbers: 5,8,14.

| <b>Decimal Number</b> | <b>Binary code</b> | BCD code  | Excess-3 code | Gray code |

|-----------------------|--------------------|-----------|---------------|-----------|

| 5                     | 0101               | 0101      | 1000          | 0111      |

| 8                     | 1000               | 1000      | 1011          | 1100      |

| 14                    | 1110               | 0001 0100 | 0100 0111     | 1001      |

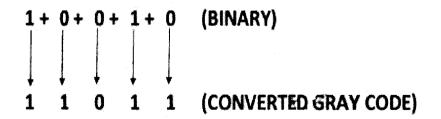

**Example 2: Binary To Gray Code Conversion**

**Example 3: Gray Code To Binary Code Conversion**

### 1.7 BOOLEAN ALGEBRA AND THEOREMS

**Ref:** 1) **A.P Godse & D.A Godse "Digital Electronics", Technical publications, Pune, Revised third** edition, 2008. Pg.No:2.1-2.10

2) Morris Mano M. and Michael D. Ciletti, "Digital Design", IV Edition, Pearson Education, 2008.Pg.No:36-44.

In 1854, George Boole developed an algebraic system now called *Boolean algebra*. In 1938, C. E. Shannon introduced a two-valued Boolean algebra called *switching algebra* that represented the properties of bistable electrical switching circuits.

Boolean algebra is an algebraic structure defined by a set of elements B, together with two binary operators. '+' and '-', provided that the following (Huntington) postulates are satisfied;

#### **Principle** of Duality

It states that every algebraic expression is deducible from the postulates of Boolean algebra, and it remains valid if the operators & identity elements are interchanged. If the inputs of a NOR gate are inverted we get a AND equivalent circuit. Similarly when the inputs of a NAND gate are inverted, we get a OR equivalent circuit.

1. Interchanging the OR and AND operations of the expression.

2. Interchanging the 0 and 1 elements of the expression.

3. Not changing the form of the variables.

#### **Theorems of Boolean algebra:**

The theorems of Boolean algebra can be used to simplify many a complex Boolean expression and also to transform the given expression into a more useful and meaningful equivalent expression. The theorems are presented as pairs, with the two theorems in a given pair being the dual of each other. These theorems can be very easily verified by the method of **\_\_perfect induction'.** According to this method, the validity of the expression is tested for all possible combinations of values of the variables involved. Also, since the validity of the theorem is based on its being true for all possible combinations of values of values of values of values, there is no reason why a variable cannot be replaced with its complement, or vice versa, without disturbing the validity. Another important point is that, if a given expression is valid, its dual will also be valid.

#### **T1: Commutative Law**

| (a) | A + B = B + A |

|-----|---------------|

| (b) | A B = B A     |

**T2:** Associative Law (a) (A + B) + C = A + (B + C)(b) (A B) C = A (B C)

#### **T3: Distributive Law**

(a) A (B + C) = A B + A C(b) A + (B C) = (A + B) (A + C)

#### **T4: Identity Law**

(a) A + A = A

(b) AA = A

# T5: Negation Law.

nu

()=

#### **T6: Redundancy**

(a) A + A B = A

(b) A(A + B) = A

#### T7: Operations with '0' & '1'

(a) 0 + A = A

(b) lA = A

(c) l + A = l

(d) 0A = 0

#### **T10: De Morgan's Theorem**

• It States that — The complement of the sum of the variables is equal to the product of the complement of each variable This theorem may+beexpressed= by the following Boolean expression.

• It states that the —Complement of the product of variables is equal to the sum of complements of each individual variable. Boolean expression for =this theorem + is

#### **Order of Precedence**

NOT operations have the highest precedence, followed by AND operations, followed by OR operations. Brackets can be used as with other forms of algebra.

e.g. X.Y + Z and X.(Y + Z) are not the same function.

#### **Truth** Tables

Truth tables are a means of representing the results of a logic function using a table. They are constructed by defining all possible combinations of the inputs to a function, and then calculating the output for each combination in turn.

| Χ | Y | $\mathbf{F}(\mathbf{X},\mathbf{Y})$ |

|---|---|-------------------------------------|

| 0 | 0 | 0                                   |

| 0 | 1 | 0                                   |

| 1 | 0 | 0                                   |

| 1 | 1 | 1                                   |

| X | F(X) |

|---|------|

| 0 | 1    |

| 1 | 0    |

| X | Y | $\mathbf{F}(\mathbf{X},\mathbf{Y})$ |

|---|---|-------------------------------------|

| 0 | 0 | 0                                   |

| 0 | 1 | 1                                   |

| 1 | 0 | 1                                   |

| 1 | 1 | 1                                   |

OR

NOT

AND

#### Minterms and maxterms

A binary variable may appear either in its normal form (x) or in its complement form (x'). Now consider two binary variables x and y combined with an AND operation. Since each variable may appear in either form, there are four possible combinations: x'y', x'y. xy', and xy. Each of these four AND term s is called a *minterm*, or a *standard product*.

In a similar fashion, n variables forming g an OR terrn with each variable being primed or Unprimed provide 2" possible combinations called *maxterm*. or *standard* sums.

• A minterm is the product of N distinct literals where each literal occurs exactly once.

• A maxterm is the sum of N distinct literals where each literal occurs exactly once.

For a two-variable expression, the minterms and maxterms are as follows

| X | Y | Minterm | Maxterm |

|---|---|---------|---------|

| 0 | 0 | X'.Y'   | X+Y     |

| 0 | 1 | X'.Y    | X+Y'    |

| 1 | 0 | X.Y'    | X'+Y    |

| 1 | 1 | X.Y     | X'+Y'   |

For a three-variable expression, the minterms and maxterms are as follows

| X | Y | Z | Minterm  | Maxterm |

|---|---|---|----------|---------|

| 0 | 0 | 0 | X'.Y'.Z' | X+Y+Z   |

| 0 | 0 | 1 | X'.Y'.Z | X+Y+Z'   |

|---|---|---|---------|----------|

| 0 | 1 | 0 | X'.Y.Z' | X+Y'+Z   |

| 0 | 1 | 1 | X'.Y.Z  | X+Y'+Z'  |

| 1 | 0 | 0 | X.Y'.Z' | X'+Y+Z   |

| 1 | 0 | 1 | X.Y'.Z  | X'+Y+Z'  |

| 1 | 1 | 0 | X.Y.Z'  | X'+Y'+Z  |

| 1 | 1 | 1 | X.Y.Z   | X'+Y'+Z' |

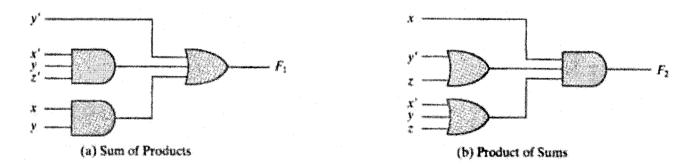

This allows us to represent expressions in either Sum of Products or Product of Sums forms

Sum Of Products (SOP): F(X, Y, ...) = Sum (ak.mk), where ak is 0 or 1 and mk is a minterm.

To derive the Sum of Products form from a truth table, OR together all of the minterms which give a value of 1.Consider the truth table as example,

| X | Y | F | Minterm |

|---|---|---|---------|

| 0 | 0 | 0 | X'.Y'   |

| 0 | 1 | 0 | X'Y     |

| 1 | 0 | 1 | X.Y'    |

| 1 | 1 | 1 | X.Y     |

Here SOP is f(X.Y) = X.Y' + X.Y

**Product Of Sum (POS):** The Product of Sums form represents an expression as a product of maxterms.F(X, Y, .....) = Product (bk + Mk), where bk is 0 or 1 and Mk is a maxterm. To derive the Product of Sums form from a truth table, AND together all of the maxterms which give a value of 0.Consider the truth table from the previous example

| X | Y | F | Maxterm |

|---|---|---|---------|

| 0 | 0 | 1 | X+Y     |

| 0 | 1 | 0 | X+Y'    |

| 1 | 0 | 1 | X'+Y    |

| 1 | 1 | 1 | X'+Y'   |

Here POS is F(X,Y) = (X+Y')

**Conversion between POS and SOP:** Conversion between the two forms is done by application of DeMorgans Laws.

#### **DIGITAL LOGIC GATES**

A logic gate is an electronic circuit/device which makes the logical decisions. To arrive at this decisions, the most common logic gates used are OR, AND, NOT, NAND, and NOR gates. The NAND and NOR gates are called universal gates. The exclusive-OR gate is another logic gate which can be constructed using AND, OR and NOT gate.

Logic gates have one or more inputs and only one output. The output is active only for certain input combinations. Logic gates are the building blocks of any digital circuit. Logic gates are also called switches. With the advent of integrated circuits, switches have been replaced by TTL (Transistor Transistor Logic) circuits and CMOS circuits. Here I give example circuits on how to construct simples gates.

•AND •OR •NOT •BUF •NAND •NOR •XOR •XNOR

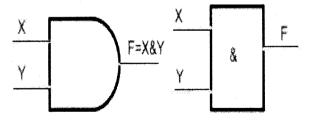

#### **AND Gate**

The AND gate performs logical multiplication, commonly known as AND function. The AND gate has two or more inputs and single output. The output of AND gate is HIGH only when all its inputs are HIGH (i.e. even if one input is LOW, Output will be LOW).

If X and Y are two inputs, then output F can be represented mathematically as F = X.Y, Here dot (.) denotes the AND operation. Truth table and symbol of the AND gate is shown in the figure below.

#### Symbol

#### Truth Table

| X | Y | $\mathbf{F}(\mathbf{X},\mathbf{Y})$ |  |

|---|---|-------------------------------------|--|

| 0 | 0 | 0                                   |  |

| 0 | 1 | 0                                   |  |

| 1 | 0 | 0                                   |  |

| 1 | 1 | 1                                   |  |

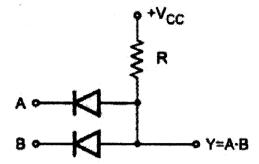

Two input AND gate using "diode-resistor" logic is shown in figure below, where X, Y are inputs and F is the output.

If X = 0 and Y = 0, then both diodes D1 and D2 are forward biased and thus both diodes conduct and pull F low.

If X = 0 and Y = 1, D2 is reverse biased, thus does not conduct. But D1 is forward biased, thus conducts and thus pulls F low.

If X = 1 and Y = 0, D1 is reverse biased, thus does not conduct. But D2 is forward biased, thus conducts and thus pulls F low.

If X = 1 and Y = 1, then both diodes D1 and D2 are reverse biased and thus both the diodes are in cut-off and thus there is no drop in voltage at F. Thus F is HIGH.

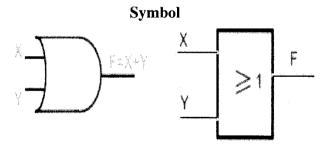

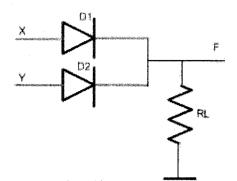

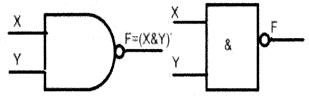

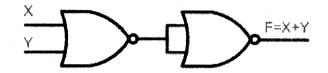

#### **OR** Gate

The OR gate performs logical addition, commonly known as OR function. The OR gate has two or more inputs and single output. The output of OR gate is HIGH only when any one of its inputs are HIGH (i.e. even if one input is HIGH, Output will be HIGH).

If X and Y are two inputs, then output F can be represented mathematically as F = X+Y. Here plus sign (+) denotes the OR operation. Truth table and symbol of the OR gate is shown in the figure below.

**Truth Table**

| X | Y | $\mathbf{F}(\mathbf{X},\mathbf{Y})$ |  |

|---|---|-------------------------------------|--|

| 0 | 0 | 0                                   |  |

| 0 | 1 | 1                                   |  |

| 1 | 0 | 1                                   |  |

| 1 | 1 | 1                                   |  |

Two input OR gate using "diode-resistor" logic is shown in figure below, where X, Y are inputs and F is the output.

If X = 0 and Y = 0, then both diodes D1 and D2 are reverse biased and thus both the diodes are in cut-off and thus F is low.

If X = 0 and Y = 1, D1 is reverse biased, thus does not conduct. But D2 is forward biased, thus conducts and thus pulling F to HIGH.

If X = 1 and Y = 0, D2 is reverse biased, thus does not conduct. But D1 is forward biased, thus conducts and thus pulling F to HIGH.

If X = 1 and Y = 1, then both diodes D1 and D2 are forward biased and thus both the diodes conduct and thus F is HIGH.

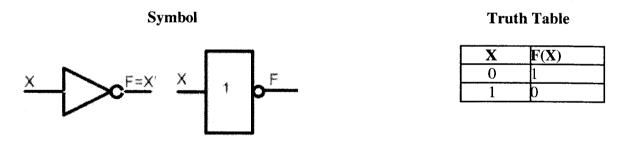

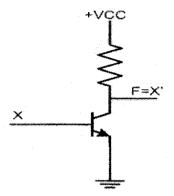

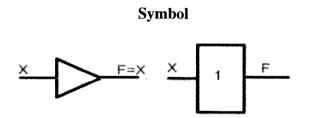

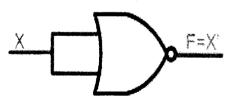

#### NOT Gate

The NOT gate performs the basic logical function called inversion or complementation. NOT gate is also called inverter. The purpose of this gate is to convert one logic level into the opposite logic level. It has one input and one output. When a HIGH level is applied to an inverter, a LOW level appears on its output and vice versa.

If X is the input, then output F can be represented mathematically as F = X', Here apostrophe (') denotes the NOT (inversion) operation. There are a couple of other ways to represent inversion, F = !X, here ! represents inversion. Truth table and NOT gate symbol is shown in the figure below.

NOT gate using "transistor-resistor" logic is shown in the figure below, where X is the input and F is the output.

When X = 1, The transistor input pin 1 is HIGH, this produces the forward bias across the emitter base junction and so the transistor conducts. As the collector current flows, the voltage drop across RL increases and hence F is LOW.

When X = 0, the transistor input pin 2 is LOW: this produces no bias voltage across the transistor base emitter junction. Thus Voltage at F is HIGH.

#### **BUF Gate**

Buffer or BUF is also a gate with the exception that it does not perform any logical operation on its input. Buffers just pass input to output. Buffers are used to increase the drive strength or sometime just to introduce delay. We will look at this in detail later.

If X is the input, then output F can be represented mathematically as F = X. Truth table and symbol of the Buffer gate is shown in the figure below.

**Truth Table**

| X | F(X) |

|---|------|

| 0 | 0    |

| 1 | 1    |

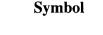

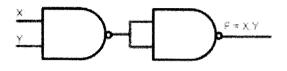

#### NAND Gate

NAND gate is a cascade of AND gate and NOT gate, as shown in the figure below. It has two or more inputs and only one output. The output of NAND gate is HIGH when any one of its input is LOW (i.e. even if one input is LOW, Output will be HIGH).

If X and Y are two inputs, then output F can be represented mathematically as F = (X.Y)', Here dot (.) denotes the AND operation and (') denotes inversion. Truth table and symbol of the N AND gate is shown in the figure below.

| Truth | Table |

|-------|-------|

|-------|-------|

| X | Y | $\mathbf{F}(\mathbf{X},\mathbf{Y})$ |

|---|---|-------------------------------------|

| 0 | 0 | 1                                   |

| 0 | 1 | 1                                   |

| 1 | 0 | 1                                   |

| 1 | 1 | 0                                   |

#### NOR Gate

NOR gate is a cascade of OR gate and NOT gate, as shown in the figure below. It has two or more inputs and only one output. The output of NOR gate is HIGH when any all its inputs are LOW (i.e. even if one input is HIGH, output will be LOW).

| X | Y | F(X,Y) |  |

|---|---|--------|--|

| 0 | 0 | 1      |  |

| 0 | 1 | 0      |  |

| 1 | 0 | 0      |  |

| 1 | 1 | 0      |  |

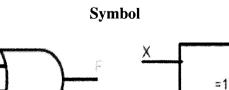

#### XOR Gate

An Exclusive-OR (XOR) gate is gate with two or three or more inputs and one output. The output of a two-input XOR gate assumes a HIGH state if one and only one input assumes a HIGH state. This is equivalent to saying that the output is HIGH if either input X or input Y is HIGH exclusively, and LOW when both are 1 or 0 simultaneously.

If X and Y are two inputs, then output F can be represented mathematically as  $F = X \square Y$ , Here  $\square$  denotes the XOR operation.  $X \square Y$  and is equivalent to X.Y' + X'.Y. Truth table and symbol of the XOR gate is shown in the figure below.

F

γ

### **Truth Table**

| X | Y | $\mathbf{F}(\mathbf{X},\mathbf{Y})$ |

|---|---|-------------------------------------|

| 0 | 0 | 0                                   |

| 0 | 1 | 1                                   |

| 1 | 0 | 1                                   |

| 1 | 1 | 0                                   |

**XNOR Gate**

An Exclusive-NOR (XNOR) gate is gate with two or three or more inputs and one output. The output of a two-input XNOR gate assumes a HIGH state if all the inputs assumes same state. This is equivalent to

saying that the output is HIGH if both input X and input Y is HIGH exclusively or same as input X and input Y is LOW exclusively, and LOW when both are not same.

If X and Y are two inputs, then output F can be represented mathematically as  $F = X \odot Y$ , Here ۲ denotes the XNOR operation.  $X \odot Y$  and is equivalent to X.Y + X'.Y'. Truth table and symbol of the XNOR gate is shown in the figure below.

Symbol

#### **Universal Gates**

Universal gates are the ones which can be used for implementing any gate like AND, OR and NOT, or any combination of these basic gates; NAND and NOR gates are universal gates. But there are some rules that need to be followed when implementing NAND or NOR based gates.

#### 1.6 NAND and NOR implementation

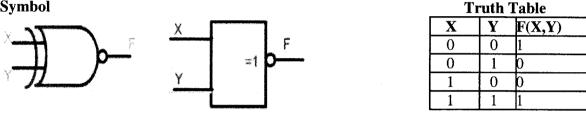

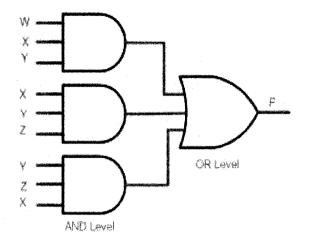

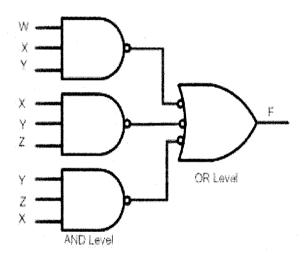

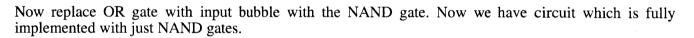

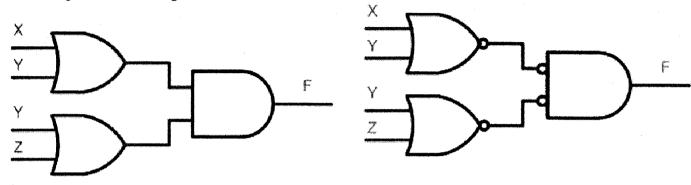

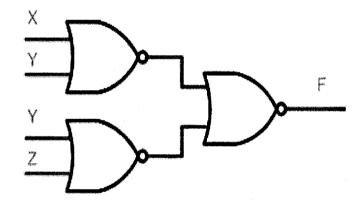

Any logic function can be implemented using NAND gates. To achieve this, first the logic function has to be written in Sum of Product (SOP) form. Once logic function is converted to SOP, then is very easy to implement using NAND gate. In other words any logic circuit with AND gates in first level and OR gates in second level can be converted into a NAND-NAND gate circuit.

Consider the following SOP expression F = W.X.Y + X.Y.Z + Y.Z.W

The above expression can be implemented with three AND gates in first stage and one OR gate in second stage as shown in figure.

# ✓ Realization of logic gates using NAND gates

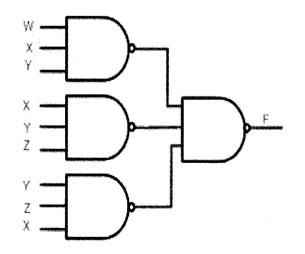

#### Implementing an inverter using NAND gate

| Input  | Output | Rule       |

|--------|--------|------------|

| (X.X)' | = X'   | Idempotent |

#### Implementing AND using NAND gates

| Input         | Output     | Rule       |

|---------------|------------|------------|

| ((XY)'(XY)')' | = ((XY)')' | Idempotent |

| -             | =(XY)      | Involution |

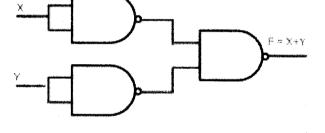

### Implementing OR using NAND gates

| Input             | Output    | Rule       |  |

|-------------------|-----------|------------|--|

| ((XX)'(YY)'<br>)' | = (X'Y')' | Idempotent |  |

|                   | ⊨ X"+Y"   | DeMorgan   |  |

|                   | = X+Y     | Involution |  |

# Implementing NOR using NAND gates

| Input                                         | Output   | Rule       |

|-----------------------------------------------|----------|------------|

| ((XX)'(YY)'<br>)'                             | =(X'Y')' | Idempotent |

| <u>,                                     </u> | =X"+Y"   | DeMorgan   |

|                                               | =X+Y     | Involution |

|                                               | =(X+Y)'  | Idempotent |

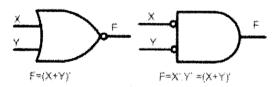

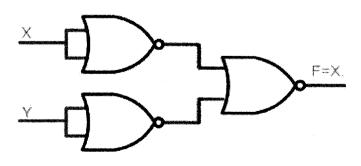

## ✓ Realization of logic function using NOR gates

Any logic function can be implemented using NOR gates. To achieve this, first the logic function has to be written in Product of Sum (POS) form. Once it is converted to POS, then it's very easy to implement using NOR gate. In other words any logic circuit with OR gates in first level and AND gates in second level can be converted into a NOR-NOR gate circuit.

Consider the following POS expression

F = (X+Y) . (Y+Z)

The above expression can be implemented with three OR gates in first stage and one AND gate in second stage as shown in figure.

If bubble are introduced at the output of the OR gates and the inputs of AND gate, the above circuit becomes as shown in figure.

Now replace AND gate with input bubble with the NOR gate. Now we have circuit which is fully implemented with just NOR gates.

Implementing an inverter using NOR gate

| Input  | Output | Rule       |

|--------|--------|------------|

| (X+X)' | = X'   | Idempotent |

# Implementing AND using NOR gates

| Input                | Output   | Rule       |

|----------------------|----------|------------|

| ((X+X)'+(Y+Y)<br>')' | =(X'+Y') | Idempotent |

|                      | = X".Y"  | DeMorgan   |

|                      | = (X.Y)  | Involution |

#### Implementing OR using NOR gates

| Input            | Output      | Rule       |

|------------------|-------------|------------|

| ((X+Y)'+(X+Y)')' | = ((X+Y)')' | Idempotent |

|                  | = X+Y       | Involution |

#### Implementing NAND using NOR gates

| Input            | Output      | Rule       |  |

|------------------|-------------|------------|--|

| ((X+Y)'+(X+Y)')' | = ((X+Y)')' | Idempotent |  |

|                  | = X+Y       | Involution |  |

|                  | = (X+Y)'    | Idempotent |  |

#### **Minimization Technique**

The primary objective of all simplification procedures is to obtain an expression that has the minimum number of terms. Obtaining an expression with the minimum number of literals is usually the secondary objective. If there is more than one possible solution with the same number of terms, the one having the minimum number of literals is the choice.

There are several methods for simplification of Boolean logic expressions. The process is usually called logic minimization and the goal is to form a result which is efficient. Two methods we will discuss are algebraic minimization and Karnaugh maps. For very complicated problems the former method can be done using special software analysis programs. Karnaugh maps are also limited to problems with up to 4 binary inputs. The Quine–McCluskey tabular method is used for more than 4 binary inputs.

#### 1.6 KARNAUGH MAPS

Maurice Karnaugh, a telecommunications engineer, developed the Karnaugh map at Bell Labs in 1953 while designing digital logic based telephone switching circuits. Karnaugh maps reduce logic functions more quickly and easily compared to Boolean algebra.

A Karnaugh map provides a pictorial method of grouping together expressions with common factors and therefore eliminating unwanted variables. The Karnaugh map can also be described as a special arrangement of a truth table.

#### **Construction of a Karnaugh Map**

**1.** Each square containing a \_1' must be considered at least once, although it can be considered as often as desired.

2. The objective should be to account for all the marked squares in the minimum number of groups.

3. The number of squares in a group must always be a power of 2, i.e. groups can have 1, 2, 4\_ 8, 16, squares.

4. Each group should be as large as possible, which means that a square should not be accounted for by itself if it can be accounted for by a group of two squares; a group of two squares should not be made if the involved squares can be included in a group of four squares and so on.

5. \_Don't care' entries can be used in accounting for all of 1-squares to make optimum groups. They are marked \_X' in the corresponding squares. It is, however, not necessary to account for all \_don't care' entries. Only such entries that can be used to advantage should be used.

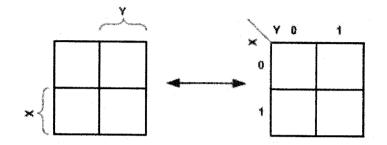

The diagram below illustrates the correspondence between the Karnaugh map and the truth table for the general case of a two variable problem.

The values inside the squares are copied from the output column of the truth table, therefore there is one square in the map for every row in the truth table. Around the edge of the Karnaugh map are the values of the two input variable. A is along the top and B is down the left hand side. The diagram below explains this:

The values around the edge of the map can be thought of as coordinates. So as an example, the square on the top right hand corner of the map in the above diagram has coordinates A=1 and B=0. This square corresponds to the row in the truth table where A=1 and B=0 and F=1. Note that the value in the F column represents a particular function to which the Karnaugh map corresponds.

#### Two variable K-map

There are four minterms for two variables: hence, the map consists of four squares, one for each minterm. In any K-Map, each square represents a minterm. Adjacent squares always differ by just one literal (So that the unifying theorem may apply: X + X' = 1). For the 2-variable case (e.g.: variables X, Y), the map can be drawn as below. Two variable map is the one which has got only two variables as input.

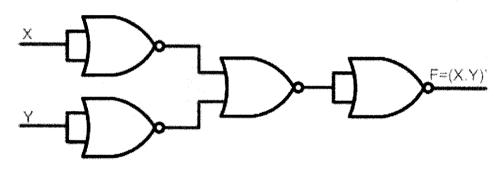

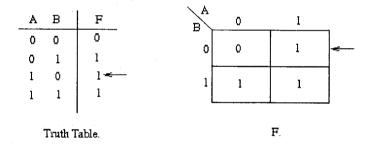

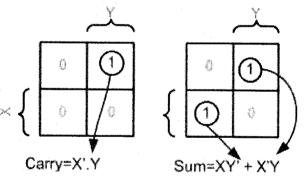

#### Example- Carry and Sum of a half adder

In this example we have the truth table as input, and we have two output functions. Generally we may have n output functions for m input variables. Since we have two output functions, we need to draw two k-maps (i.e. one for each function). Truth table of 1 bit adder is shown below. Draw the k-map for Carry and Sum as shown below.

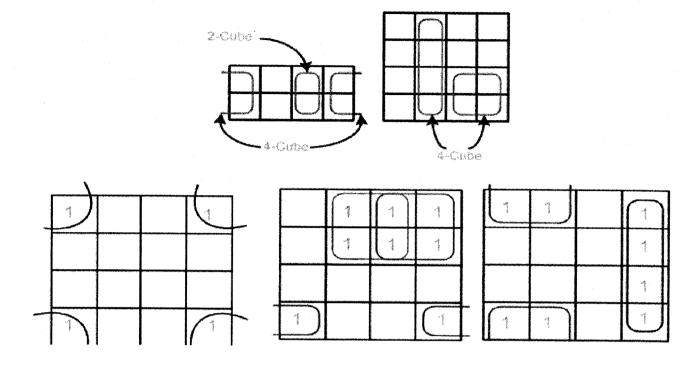

### **Grouping/Circling K-maps**

The power of K-maps is in minimizing the terms, K-maps can be minimized with the help of grouping the terms to form single terms. When forming groups of squares, observe/consider the following:

• Every square containing 1 must be considered at least once.

- A square containing 1 can be included in as many groups as desired.

- A group must be as large as possible.

• If a square containing 1 cannot be placed in a group, then leave it out to include in final expression.

• The number of squares in a group must be equal to 2 .i.e. 2,4,8,.

• The map is considered to be folded or spherical, therefore squares at the end of a row or column are treated as adjacent squares.

• The simplified logic expression obtained from a K-map is not always unique. Groupings can be made in different ways.

• Before drawing a K-map the logic expression must be in canonical form.

**Example of invalid groups**

**Example (1)- X'Y+XY:** In this example we have the equation as input, and we have one output function. Draw the k-map for function F with marking 1 for X'Y and XY position. Now combine two 1's as shown in figure to form the single term. As you can see X and X' get canceled and only Y remains

**Example (2)- X'Y+XY+XY' :**In this example we have the equation as input, and we have one output function. Draw the k-map for function F with marking 1 for X'Y, XY and XY position. Now combine two 1's as shown in figure to form the two single terms.

$\mathbf{F} = \mathbf{X} + \mathbf{Y}$

#### **3-Variable K-Map**

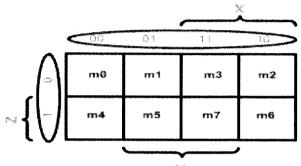

There are 8 minterms for 3 variables (X, Y, Z). Therefore, there are 8 cells in a 3-variable K-map. One important thing to note is that K-maps follow the gray code sequence, not the binary one. Each cell in a 3-variable K-map has 3 adjacent neighbours. In general, each cell in an n-variable K-map has n adjacent neighbours.

There is wrap-around in the K-map

• X'Y'Z' (m0) is adjacent to X'YZ' (m2)

• XY'Z' (m4) is adjacent to XYZ' (m6)

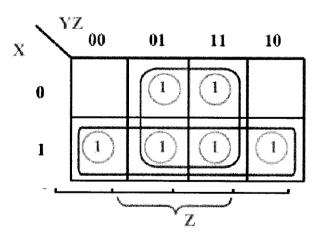

**Example (4)**  $F(X,Y,Z) = \blacksquare (1,3,4,5,6,7)$

**Example (3)**

$$F = XYZ'+XYZ+X'YZ$$

F = XY + YZ

# F = X + Z

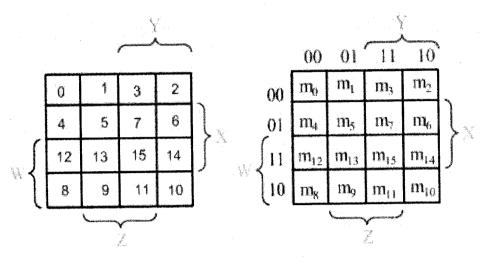

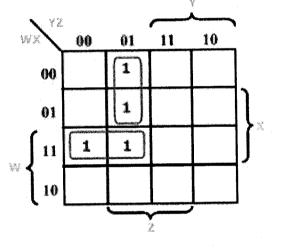

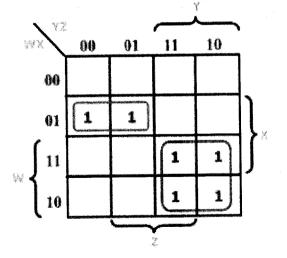

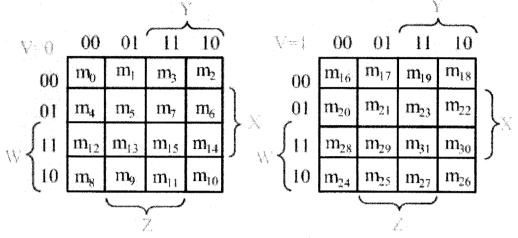

4-Variable K-Map: There are 16 cells in a 4-variable (W, X, Y, Z); K-map as shown in the figure below

**Example (5)** F(W,X,Y,Z) = (1,5,12,13)

**Example (6)** F(W,X,Y,Z) = (4, 5, 10, 11, 14, 15)

5-Variable K-Map: There are 32 cells in a 5-variable (V, W, X, Y, Z); K-map as shown in the figure below.

### 1.7 QUINE- MCCLUSKEY METHOD

The tabular method which is also known as the Quine-McCluskey method is particularly useful when minimising functions having a large number of variables, e.g. The six-variable functions. Computer programs have been developed employing this algorithm. The method reduces a function in standard sum of products form to a set of prime implicants from which as many variables are eliminated as possible. These prime implicants are then examined to see if some are redundant.

The tabular method makes repeated use of the law  $A + \blacksquare = 1$ . Note that Binary notation is used for the function, although decimal notation is also used for the functions. As usual a variable in true form is denoted by 1, in inverted form by 0, and the abscence of a variable by a dash (-).

#### **Rules of Tabular Method**

- 1. The Boolean expression to be simplified is expanded if it is not in expanded form.

- 2. Different terms in the expression are divided into groups depending upon the number of 1s they have.

- 3. The terms of the first group are successively matched with those in the next adjacent higher order group to look for any possible matching and consequent reduction. The terms are considered matched when all literals except for one match. The pairs of matched terms are replaced with a single term where the position of the unmatched literals is replaced with a dash (---). These new terms. formed as a result of the matching process find a place in the second table. The terms in the first table that do not find a match are called the prime implicants and are marked with an asterisk (). The matched terms are ticked (\_\_).

- 4. Terms in the second group are compared with those in the third group to look for a possible match.

Again, terms in the second group that do not find a match become the prime implicants.

- 5. The process continues until we reach the last group. This completes the first round of matching. The terms resulting from the matching in the first round are recorded in the second table.

- 6. The next step is to perform matching operations in the second table. While comparing the terms for a match, it is important that a dash (—) is also treated like any other literal, that is, the dash signs also need to match. The process continues on to the third table, the fourth tables and so on until the terms become irreducible any further.

- 7. An optimum selection of prime implicants to account for all the original terms constitutes the terms for the minimized expression. Although optional (also called <u>\_do 't care') ter s are</u> considered for matching, they do not have to be accounted for once prime implicants have been identified.

Example 1: Let us consider an example. Consider the following sum-of-products expression:

$$\overline{A}.B.C + \overline{A}.\overline{B}.D + A.\overline{C}.D + B.\overline{C}.\overline{D} + \overline{A}.B.\overline{C}.D$$

In the first step, we write the expanded version of the given expression. It can be written as follows:

# $\overline{A}.B.C.D + \overline{A}.B.C.\overline{D} + \overline{A}.\overline{B}.C.D + \overline{A}.\overline{B}.\overline{C}.D + A.B.\overline{C}.D + A.\overline{B}.\overline{C}.D + A.B.\overline{C}.\overline{D} + \overline{A}.B.\overline{C}.\overline{D} + \overline{A}.B.\overline{C}.D$

The formation of groups, the placement of terms in different groups and the first-round matching are shown as follows:

| A | В | С | D | Α | В | C | D                                      |              | Α | В | С              | D |      |

|---|---|---|---|---|---|---|----------------------------------------|--------------|---|---|----------------|---|------|

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1                                      |              | 0 | 0 | <b>1</b> 00000 | 1 | <br> |

| 0 | 0 | 1 | 1 | 0 | Î | 0 | 0                                      | 4            | 0 |   | 0              | 1 | 1    |

| 0 | 1 | 0 | 0 |   |   |   |                                        |              |   | 0 | 0              | 1 | 5    |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1                                      | 1            | 0 | 1 | 0              |   | 1    |

| 0 | 1 |   | 0 | 0 | l | 0 | l                                      | 1            | 0 | 1 | <b>61454</b>   | 0 | 1    |

| 0 | 1 | ł | 1 | 0 | t | 1 | 0                                      | 1            |   | 1 | 0              | 0 | 1    |

| 1 | 0 | 0 | 1 | L | 0 | 0 | L                                      | 1            |   |   |                |   |      |

| ľ | 1 | 0 | 0 | I | I | 0 | 0                                      | $\checkmark$ | 0 | - | 1              | 1 | 1    |

| 1 | 1 | 0 | l | 0 | 1 | ł | 1                                      | ~            | 0 | 1 | -              | 1 | 1    |

|   |   |   |   | t | L | 0 | 1                                      | 1            |   | 1 | 0              | 1 | 1    |

|   |   |   |   |   |   |   | #************************************* |              | 0 | 1 | 1              |   | 1    |

|   |   |   |   |   |   |   |                                        |              | 1 |   | Ô              | 1 |      |

1

1.

0

The second round of matching begins with the table shown on the previous page. Each term in the first

group is compared with every term in the second group. For instance, the first term in the first group 00-1 matches with the second term in the second group 01-1 to yield 0--1, which is recorded in the table shown below. The process continues until all terms have been compared for a possible match. Since this new table has only one group, the terms contained therein are all prime implicants.

In the present example, the terms in the first and second tables have all found a match. But that is not always the case.

|   | D | С      | B | A      |

|---|---|--------|---|--------|

| * | t | #1.000 |   | 0      |

| * | 1 | 0      |   | -<br>- |

| * |   |        | 1 | 0      |

| * |   | 0      | 1 |        |

The next table is what is known as the prime implicant table. The prime implicant table contains all the original terms in different columns and all the prime implicants recorded in different rows as shown below:

| 0001           | 0011 | 0100     | 0101         | 0110         | 0111 | 1001 | 1100 | 1101     |     |                                   |

|----------------|------|----------|--------------|--------------|------|------|------|----------|-----|-----------------------------------|

| √ <sup>2</sup> | 1    |          | <b>v</b>     |              | 1    |      |      |          | 01  | $P \rightarrow \overline{A}.D$    |

| <b>V</b>       |      |          | <b>v</b>     |              |      | V    |      | 1        | 01  | $Q \rightarrow \overline{C}.D$    |

|                |      | ¥-       | ¥ .          | $\checkmark$ | 1    |      |      |          | 01  | $\overline{R} \to \overline{A}.B$ |

|                |      | <b>v</b> | $\checkmark$ |              |      |      | 1    | <b>V</b> | -10 | $S \rightarrow B.\overline{C}$    |

Each prime implicant is identified by a letter. Each prime implicant is then examined one by one and the terms it can account for are ticked as shown. The next step is to write a product-of-sums expression using the prime implicants to account for all the terms. In the present illustration, it is given as follows.

$$(P+Q).(P).(R+S).(P+Q+R+S).(R).(P+R).(Q).(S).(Q+S)$$

Obvious simplification reduces this expression to PQRS which can be interpreted to mean that all prime implicants, that is, P, Q, R and S, are needed to account for all the original terms.

Therefore, the minimized expression =  $\overline{A}.D + \overline{C}.D + \overline{A}.B + B.\overline{C}$ .

# Example 2: $(\overline{A} + \overline{B} + \overline{C} + \overline{D}).(\overline{A} + \overline{B} + \overline{C} + D).(\overline{A} + \overline{B} + C + \overline{D}).(A + \overline{B} + \overline{C} + \overline{D}).(A + \overline{B} + C + \overline{D})$

The procedure is similar to that described for the case of simplification of sum-of-products expressions. The resulting tables leading to identification of prime implicants are as follows:

| A   |     | C |    | A      | B  | C      | D |        | A | B  | ~ | D |          | A       |   | C | Ď |         |

|-----|-----|---|----|--------|----|--------|---|--------|---|----|---|---|----------|---------|---|---|---|---------|

| 0   | 1   | 0 | 1  | 0      | I. | 0      | I | s.     | 0 | £. | - | 1 | 1        | 2000    | 1 |   | 1 | *       |

| 0   | t   | 1 | Ì  |        |    | ****** |   |        | - | I  | 0 | 1 | 1        | ******* |   |   |   | <u></u> |

| 1   | 1   | Ó | 1  | 0      | 1  | 1      | 1 | 1      |   | -  | - | - | ~        |         |   |   |   |         |

| . 1 | . 1 | 1 | 0  | 1      | 1  | 0      | 1 | 1      |   | 1  | l | 1 | ~        |         |   |   |   |         |

|     | 1   | 1 | L. | 1      | 1  | 1      | 0 | 1      | 1 | 1  |   | 1 | <b>V</b> |         |   |   |   |         |

|     |     |   |    | ****** |    |        |   | ****** | 1 | 1  | I |   | 4        |         |   |   |   |         |

|     |     |   |    | 1      | 1  | 1      | 1 | L      |   |    |   |   |          |         |   |   |   |         |

The prime implicant table is constructed after all prime implicants have been identified to look for the optimum set of prime implicants needed to account for all the original terms. The prime implicant table shows that both the prime implicants are the essential ones:

| 0101 | 0111 | 1101 | 1110 | 1111     | Prime implicants |

|------|------|------|------|----------|------------------|

|      |      |      | . 🗸  | ~        | 111-             |

| 1    | × .  | ×    |      | <b>√</b> |                  |

The minimized expression =  $(\overline{A} + \overline{B} + \overline{C}).(\overline{B} + \overline{D}).$

**Example 3:**Consider the function f(A, B, C, D) = (0,1,2,3,5,7,8,10,12,13,15), note that this is in decimal form.

(0000,0001,0010,0011,0101,0111,1000,1010,1100,1101,1111) in binary form. (0,1,1,2,2,3,1,2,2,3,4) in the index form.

The prime implicants are: -+-++ + + The chart is used to remove redundant prime implicants. A grid is prepared having all the prime implicants listed at the left and all the minterms of the function along the top. Each minterm covered by a given prime implicant is marked in the appropriate position.

+ - +

From the above chart, BD is an essential prime implicant. It is the only prime implicant that covers the minterm decimal 15 and it also includes 5, 7 and 13. So an essential prime implicant. It is the only prime implicant that covers the minterm denoted by decimal 10 and it also includes the terms 0, 2 and 8. The other minterms of the function are 1, 3 and 12. Minterm 1 is present in and D. Similarly for minterm 3, We can therefore use either of these prime implicants for these minterms. Minterm 12 is present in A and AB , so again either can be used.

Thus, one minimal solution is:

UNIT II Arithematic circuits Half adder – Truth table and circuit – Full adder – Truth table and circuit – Four bit adder – Half subtractor – Full subtractor – Multiplexer: Four input multiplexer – Applications of Multiplexer – demultiplexer – Decoders 2 to 4 decoder – BCD to seven segment decoder – encoders.

Arithmetic circuits are the ones which perform arithmetic operations like addition, subtraction, multiplication, division, parity calculation. Most of the time, designing these circuits is the same as designing mux, encoders and decoders.

+

#### 1. Adders

Adders are the basic building blocks of all arithmetic circuits; adders add two binary numbers and give out sum and carry as output. Basically we have two types of adders.

- Half Adder.

- Full Adder.

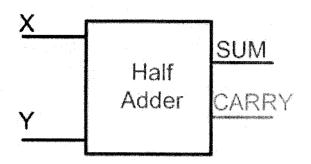

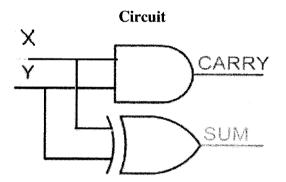

- ✓ Half Adder

A half-adder is an arithmetic circuit block that can be used to add two bits. Such a circuit thus has two inputs that represent the two bits to be added and two outputs, with one producing the SUM output and the other producing the CARRY.

Adding two single-bit binary values X, Y produces a sum S bit and a carry out C-out bit. This operation is called half addition and thus the circuit to realize it is called a half adder.

#### Symbol

Truth table

| X | Y | SUM | CARRY |

|---|---|-----|-------|

| 0 | 0 | 0   | ρ     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

The expression for the sum and carry are,

Sum = XY + XY

Carry = XY

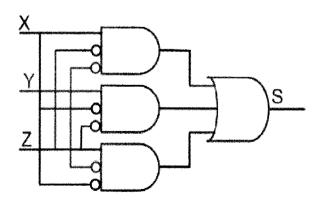

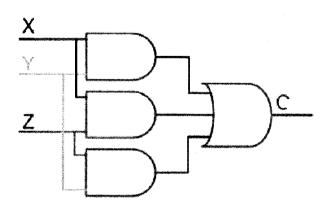

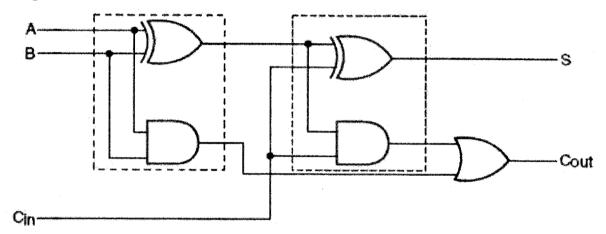

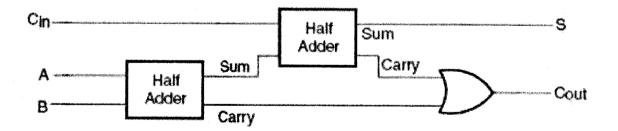

#### ✓ Full Adder

A full adder circuit is an arithmetic circuit block that can be used to add three bits to produce a SUM and a CARRY output. Such a building block becomes a necessity when it comes to adding binary numbers with a large number of bits. The full adder circuit overcomes the limitation of the half-adder, which can be used to add two bits only.

Full adder takes a three-bits input. Adding two single-bit binary values X, Y with a carry input bit C-in produces a sum bit S and a carry out C.

#### **Truth Table**

| X | Y | Z | SU<br>M | CARRY |

|---|---|---|---------|-------|

| 0 | 0 | 0 | 0       | 0     |

| 0 | 0 | 1 | 1       | 0     |

| 0 | 1 | 0 | 1       | 0     |

| 0 | 1 | 1 | 0       | 1     |

| 1 | 0 | 0 | 1       | 0     |

| 1 | 0 | 1 | 0       | 1     |

| 1 | 1 | 0 | 0       | 1     |

| 1 | 1 | 1 | 1       | 1     |

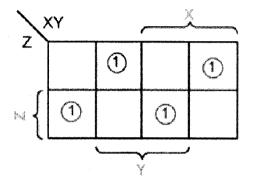

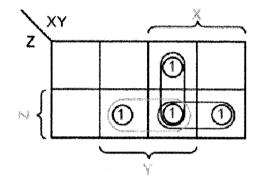

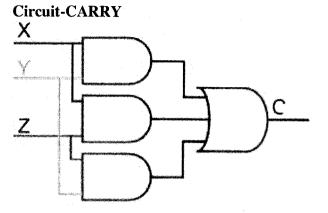

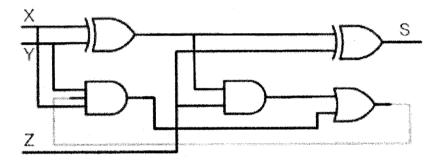

# Full Adder using AND-OR

The below implementation shows implementing the full adder with AND-OR gates, instead of using XOR gates. The basis of the circuit below is from the above K-map

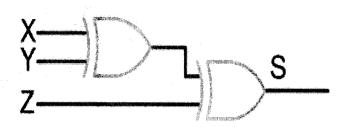

**Circuit-SUM**

=

**Circuit-CARRY**

Full Adder using AND-OR

**Circuit-SUM**

Logic Implementation of a full adder with Half Adders

✓ n-bit Carry Ripple Adder

An n-bit adder used to add two n-bit binary numbers can be built by connecting n full adders in series. Each full adder represents a bit position j (from 0 to n-1).

Each carry out C-out from a full adder at position j is connected to the carry in C-in of the full adder at higher position j+1. The output of a full adder at position j is given by:

In the expression of the sum Cj must be generated by the full adder at lower position j. The propagation delay in each full adder to produce the carry is equal to two gate delays = 2 D Since the generation of the sum requires the propagation of the carry from the lowest position to the highest position, the total propagation delay of the adder is approximately:

Total Propagation delay = 2 nD

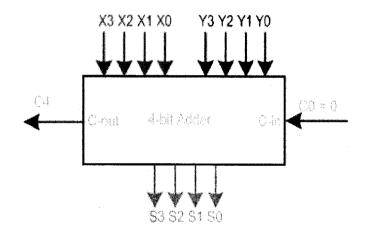

#### 4-bit Carry Ripple Adder

Adds two 4-bit numbers:

# $\dot{\mathbf{X}} = \mathbf{X3} \ \mathbf{X2} \ \mathbf{X1} \ \mathbf{X0}$

Y = Y3 Y2 Y1 Y0

Producing the sum S = S3 S2 S1 S0, C-out = C4 from the most significant position j=3 Total Propagation delay = 2 nD = 8D or 8 gate delays

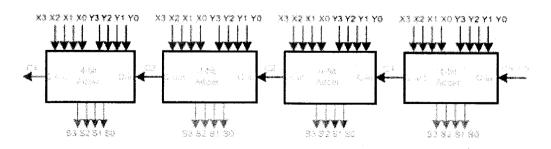

#### Larger Adder

Example: 16-bit adder using 4 4-bit adders. Adds two 16-bit inputs X (bits X0 to X15), Y (bits Y0 to Y15) producing a 16-bit Sum S (bits S0 to S15) and a carry out C16 from the most significant position. Propagation delay for 16-bit adder = 4 x propagation delay of 4-bit adder =  $4 \times 2 \text{ nD} = 4 \times 8D = 32 \text{ D}$  or 32 gate delays

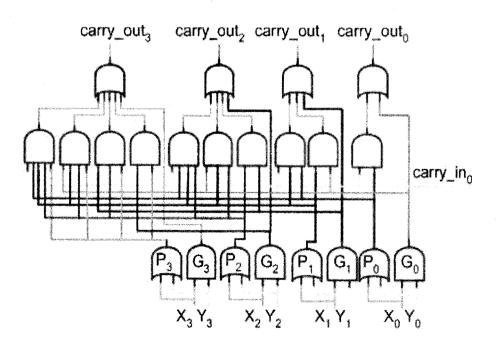

Carry Look-Ahead Adder

The delay generated by an N-bit adder is proportional to the length N of the two numbers X and Y that are added because the carry signals have to propagate from one full-adder to the next. For large values of N, the delay becomes unacceptably large so that a special solution needs to be adopted to accelerate the calculation of the carry bits. This solution involves a "look-ahead carry generator" which is a block that simultaneously calculates all the carry bits involved. Once these bits are available to the rest of the circuit, each individual three-bit addition (Xi+Yi+carry-ini) is implemented by a simple 3-input XOR gate. The design of the look-ahead carry generator involves two Boolean functions named Generate and Propagate. For each input bits pair these functions are defined as:  $Gi = Xi \cdot Yi \& Pi = Xi + Yi$

The carry bit c-out(i) generated when adding two bits Xi and Yi is '1' if the corresponding function Gi is '1' or if the c-out(i-1)='1' and the function Pi = '1' simultaneously. In the first case, the carry bit is activated by the local conditions (the values of Xi and Yi). In the second, the carry bit is received from the less significant elementary addition and is propagated further to the more significant elementary addition. Therefore, the carry\_out bit corresponding to a pair of bits Xi and Yi is calculated according to the equation:

$carry_out(i) = Gi + Pi.carry_in(i-1)$

For a four-bit adder the carry-outs are calculated as follows

$carry\_out0 = G0 + P0 . carry\_in0$   $carry\_out1 = G1 + P1 . carry\_out0 = G1 + P1G0 + P1P0 . carry\_in0$   $carry\_out2 = G2 + P2G1 + P2P1G0 + P2P1P0 . carry\_in0$  $carry\_out3 = G3 + P3G2 + P3P2G1 + P3P2P1G0 + P3P2P1 . carry\_in0$

The set of equations above are implemented by the circuit below and a complete adder with a lookahead carry generator is next. The input signals need to propagate through a maximum of 4 logic gate in such an adder as opposed to 8 and 12 logic gates in its counterparts illustrated earlier.

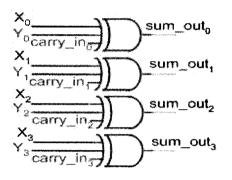

Sums can be calculated from the following equations, where carry\_out is taken from the carry calculated in the above circuit.

sum\_out0 = X 0 Y0

carry\_out0 sum\_out1 = X 1 Y1

carry\_out1 sum\_out2 = X 2 Y2

carry\_out2 sum\_out3 = X 3 Y3

carry\_out3

#### ✓ BCD Adder

BCD addition is the same as binary addition with a bit of variation: whenever a sum is greater than 1001, it is not a valid BCD number, so we add 0110 to it, to do the correction. This will produce a carry, which is added to the next BCD position.

• Add the two 4-bit BCD code inputs.

• Determine if the sum of this addition is greater than 1001; if yes, then add 0110 to this sum and generate a carry to the next decimal position

#### 2. Subtractor

Subtractor circuits take two binary numbers as input and subtract one binary number input from the other

binary number input. Similar to adders, it gives out two outputs, difference and borrow (carry-in the case of Adder). The BORROW output here specifies whether a 1' has been borrowed to perform the

subtraction.

There are two types of subtractors,

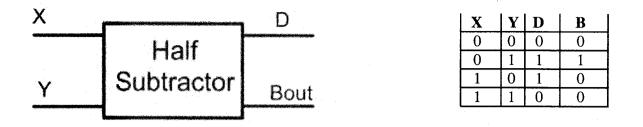

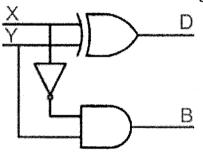

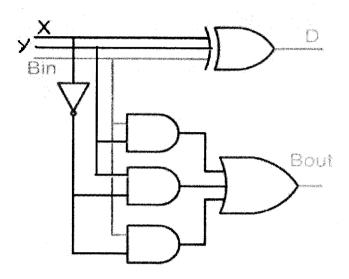

#### ✓ Half Subtractor

The half-subtractor is a combinational circuit which is used to perform subtraction of two bits. It has two inputs, X (minuend) and Y (subtrahend) and two outputs D (difference) and B (borrow). The logic symbol and truth table are shown below.

#### Symbol

Truth table

From the above table we can draw the K-map as shown below for "difference" and "borrow". The Boolean expression for the difference and Borrow can be written.

From the equation we can draw the half-subtractor as shown in the figure below.

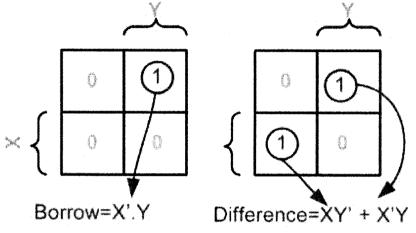

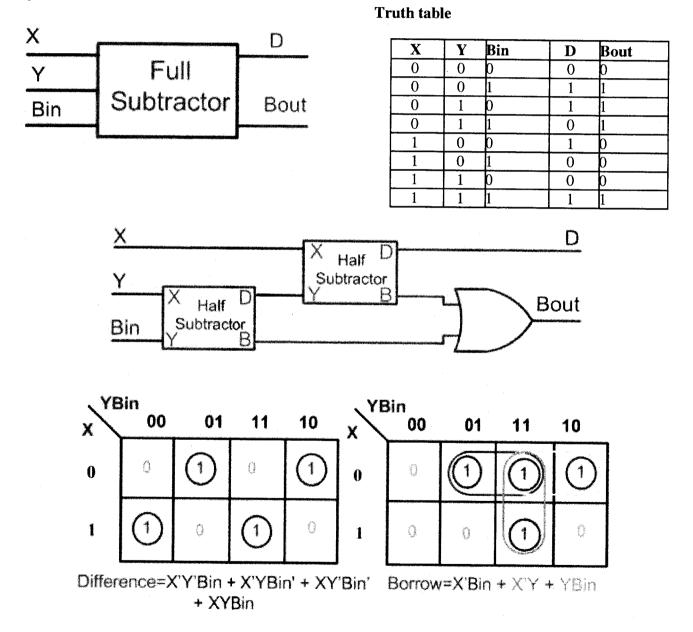

# ✓ Full Subtractor

A full subtractor is a combinational circuit that performs subtraction involving three bits, namely

minuend, subtrahend, and borrow-in. There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo. The BORROW output bit tells whether the minuend bit needs to borrow a  $\_1^{\circ}$

1' from the next possible higher minuend bit. The logic symbol and truth table are shown below. Symbol

From the above expression, we can draw the circuit below. If you look carefully, you will see that a full-subtractor circuit is more or less same as a full-adder with slight modification.

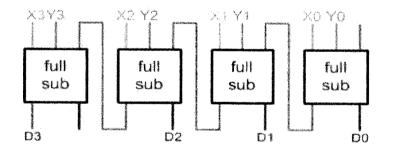

# Parallel Binary Subtractor

$\checkmark$

Parallel binary subtractor can be implemented by cascading several full-subtractors. Implementation and associated problems are those of a parallel binary adder, seen before in parallel binary adder section.

Below is the block level representation of a 4-bit parallel binary subtractor, which subtracts 4-bit Y3Y2Y1Y0 from 4-bit X3X2X1X0. It has 4-bit difference output D3D2D1D0 with borrow output Bout.

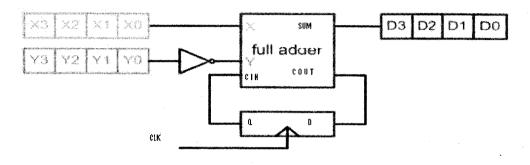

## ✓ Serial Binary Subtracter

A serial subtracter can be obtained by converting the serial adder using the 2's complement system. The subtrahend is stored in the Y register and must be 2's complemented before it is added to the minuend stored in the X register. The circuit for a 4-bit serial subtracter using full-adder is shown in the figure below.

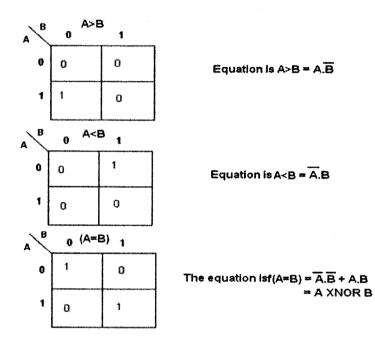

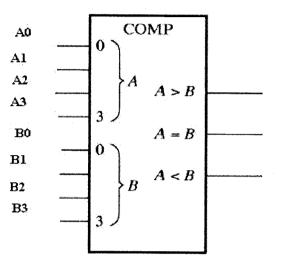

## ✓ Comparators

It is a combinational circuit that compares two numbers and determine their relative magnitude. The output of comparator is usually 3 binary variables indicating:

## A<B, A=B, A>B

**1-bit comparator: Let's** begin with 1 bit comparator and from the name we can easily make out that this circuit would be used to compare 1 bit binary numbers.

| Α | B | A>B | A=B | A <b< th=""></b<> |

|---|---|-----|-----|-------------------|

| 0 | 0 | 0   | 1   | 0                 |

| 1 | 0 | 1   | 0   | 0                 |

| 0 | 1 | 0   | 0   | 1                 |

| 1 | 1 | 0   | 1   | 0                 |

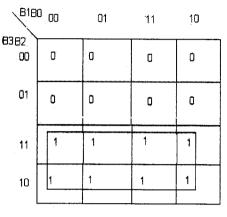

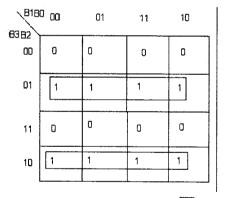

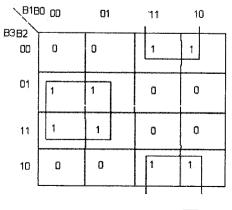

For a 2-bit comparator we have four inputs A1A0 and B1B0 and three output E ( is 1 if two numbers are equal) G (is 1 when A > B) and L (is 1 when A < B) If we use truth table and K-map the result is

The comparison process of two positive numbers X and Y is performed in a bit-by-bit manner starting with the most significant bit:

If the most significant bits are Xn='1' and Yn='0' then number X is larger than Y.

- If Xn='0' and Yn='1' then number X is smaller than Y.

- If Xn=Yn then no decision can be taken about X and Y based only on these two bits.

If the most significant bits are equal then the result of the comparison is determined by the less significant bits Xn-1 and Yn-1. If these bits are equal as well, the process continues with the next pair of bits. If all bits are equal then the two numbers are equal.

# 4-bit comparator:

# 2.5 CODE CONVERSION- Binary to Gray converter

# **Truth Table**

| S. No | <b>B3</b> | <b>B2</b> | <b>B</b> 1 | BO | G3 | <b>G2</b> | <b>G1</b> | GO |

|-------|-----------|-----------|------------|----|----|-----------|-----------|----|

| 0     | 0         | 0         | 0          | 0  | 0  | 0         | 0         | 0  |

| 1     | 0         | 0         | 0          | 1  | 0  | 0         | 0         | 1  |

| 2     | 0         | 0         | 1          | 0  | 0  | 0         | 1         | 1  |

| 3     | 0         | 0         | 1          | 1  | 0  | 0         | 1         | 0  |

| 4     | 0         | 1         | 0          | 0  | 0  | 1         | 1         | 0  |

| 5     | 0         | 1         | 0          | 1  | 0  | 1         | 1         | 1  |

| 5     | 0         | 1         | 1          | 0  | 0  | 1         | 0         | 1  |

| 7     | 0         | 1         | 1          | 1  | 0  | 1         | 0         | 0  |

| 8     | 1         | 0         | 0          | 0  | 1  | 1         | 0         | 0  |

| 9     | 1         | 0         | 0          | 1  | 1  | 1         | 0         | 1  |

| 10    | 1         | 0         | 1          | 0  | 1  | 1         | 1         | 1  |

| 11    | 1         | 0         | 1          | 1  | 1  | 1         | 1         | 0  |

| 12    | 1         | 1         | 0          | 0  | 1  | 0         | 1         | 0  |

| 13    | 1         | 1         | 0          | 1  | 1  | 0         | 1         | 1  |

| 14    | 1         | 1         | 1          | 0  | 1  | 0         | 0         | 1  |

| 15    | 1         | 1         | 1          | 1  | 1  | 0         | 0         | 0  |

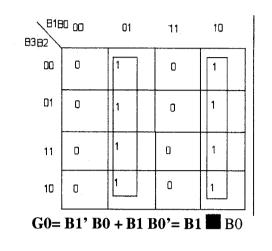

# K-MAP FOR G3:

G3= B3

# K-MAP FOR G2:

G2= B3' B2 + B3 B2'= B3 B2

# K-MAP FOR G1:

G1= **B1'** B2 + B1 **B2'=** B1 **B**2

### **K-MAP FOR G0**

G3 G3 G1 G0 G3 B3 B2 B2 B1 B1 B0 B0

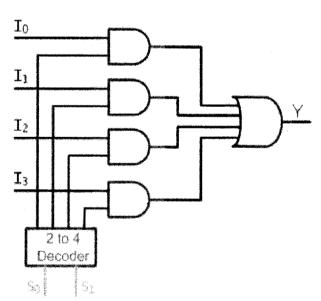

## 2.6 DECODERS

A **decoder** circuit can be used to implement AND-OR circuit SOP Boolean expression when decoder active state output is 1 and inactive 0.

- Number of binary inputs = n

- Number of binary outputs = 2n = Maximum number of minterms, where n is the number of literals in F

- Its outputs reflect the Mini-terms with one term each at each of the output

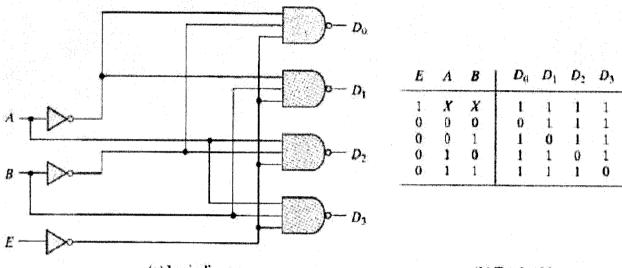

(a) Logic diagram

(b) Truth table

# Figure: 2-to-4 line decoder with enable input

|    | Inputs |   |    |    |                | Out | puts |    |                |   |

|----|--------|---|----|----|----------------|-----|------|----|----------------|---|

| X  | y      | 2 | Do | D1 | D <sub>2</sub> | D3  | D4   | Ds | D <sub>6</sub> | D |

| 0  | 0      | 0 | 1  | 0  | 0              | 0   | 0    | 0  | 0              | 0 |

| 0  | 0      | 1 | 0  | Ĩ. | 0              | 0   | 0    | 0  | 0              | õ |

| 0  | 1      | 0 | 0  | 0  | 1              | 0   | 0    | 0  | 0              | 0 |

| 0  | 1      |   | .0 | 0  | 0              | 1   | 0    | 0  | 0              | 0 |

| 1  | 0      | 0 | 0  | 0  | 0              | 0   | 1    | 0  | ō              | Ő |

| 1  | 0      | 1 | 0  | 0  | 0              | 0   | 0    | Ĩ  | 0              | õ |

| I. | 1      | 0 | Ö  | 0  | 0              | 0   | 0    | Ó  | 1              | Ō |

| 1  | 1      | 1 | 0  | Ő  | 0              | 0   | 0    | 0  | Ő              | Ĩ |

Truth Table of a Three-to-Eight-Line Decoder

Fig: Circuit for 3-to-8 line decoder

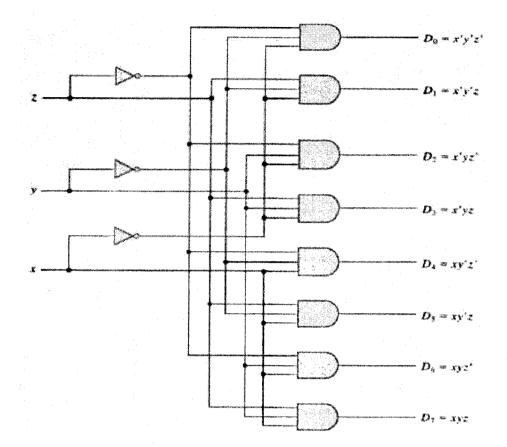

# 2.7 ENCODERS

An **encoder** is a circuit that converts the binary information from one form to another. Gives a unique combination of outputs according to the information at a unique input at one-line (or at multiple lines). Action of a one active line input encoder is opposite of that of a one active line output decoder. An encoder, which has multi-lines as the active inputs, is also called 'priority encoder'. Encoder can be differentiated from decoder by greater number of inputs than outputs compared to the decoder. The priority encoder includes a priority function.

**4to3 Priority Encoder**-The truth table of a 4-input priority encoder is as shown below. The input D3 has the highest priority, D2 has next highest priority, D0 has the lowest priority. This means output Y2 and Y1 are 0 only when none of the inputs D1, D2, D3 are high and only D0 is high. A 4 to 3 encoder consists of four inputs and three outputs, truth table and symbols of which is shown below. **Truth Table**

| D3 | Dź | 2 | D1 | D | 0 | Y2 | Y1 | YO | ٦ |

|----|----|---|----|---|---|----|----|----|---|

| 0  | 0  | C | )  | 0 |   | 0  | 0  | 0  |   |

|    |    |   |    |   |   |    |    |    |   |

|    |    |   |    |   |   |    |    |    |   |

|    |    |   |    |   |   |    |    |    |   |

|    |    |   |    |   |   |    |    |    |   |

|    |    |   |    |   |   |    |    |    |   |

| 0  | 0  | c | )  | 1 |   | þ  | о  | 1  |   |

| 6  |    | 0 | 1  |   | x | 0  |    | 0  |   |

| 0  |    | 1 | x  | + | x | 0  | 1  | 1  |   |

| 1  |    | X | x  |   | x | 1  | 0  | 0  |   |

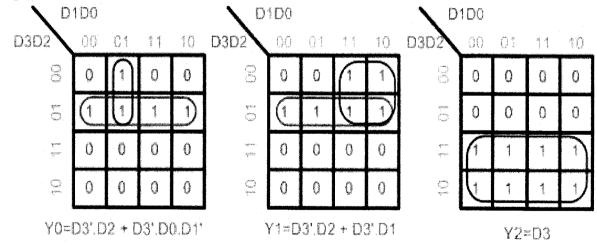

K-map

# 2.8 MULTIPLEXERS

Many tasks in communications, control, and computer systems can be performed by combinational logic circuits. When a circuit has been designed to perform some task in one application, it often finds use in a different application as well.

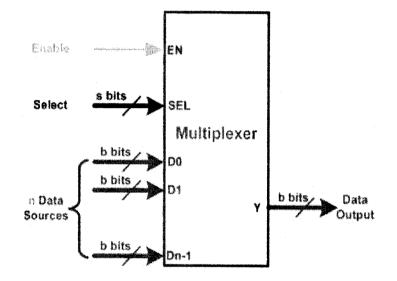

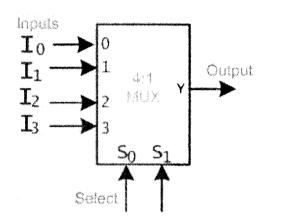

A **multiplexer** (**MUX**) is a digital switch which connects data from one of n sources to the output. A number of select inputs determine which data source is connected to the output. The block diagram of MUX with n data sources of b bits wide and s bits wide select line is shown in below figure.

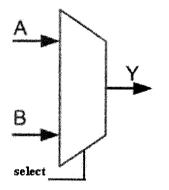

### Example - 2x1 MUX

A 2 to 1 line multiplexer is shown in figure below, each 2 input lines A to B is applied to one input of an AND gate. Selection lines S are decoded to select a particular AND gate. The truth table for the 2:1 mux is given in the table below.

#### **Truth table**

| S | Y |

|---|---|

| 0 | А |

| 1 | В |

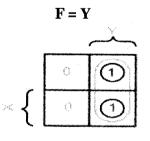

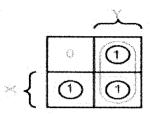

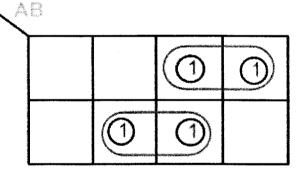

## Design of a 2:1 Mux

To derive the gate level implementation of 2:1 mux we need to have truth table as shown in figure. And once we have the truth table, we can draw the K-map as shown in figure for all the cases when Y is equal to 'I'.

Combining the two 1' as shown in figure, we can drive the output y as shown below

Y = A.S' + B.S

| Truth table |

|-------------|

|-------------|

| B | A | S | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

200 100

## Example : 4:1 MUX

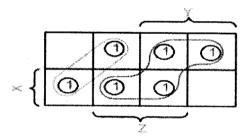

A 4 to 1 line multiplexer is shown in figure below, each of 4 input lines I0 to I3 is applied to one input of an AND gate. Selection lines S0 and S1 are decoded to select a particular AND gate. The truth table for the 4:1 mux is given in the table below.

Truth table

| S1 | S0 | Y  |

|----|----|----|

| 0  | 0  | IO |

| 0  | 1  | I1 |

| 1  | 0  | I2 |

| 1  | 1  | 13 |

Circuit

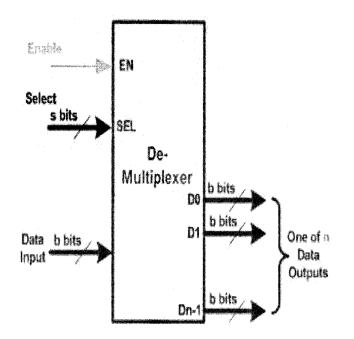

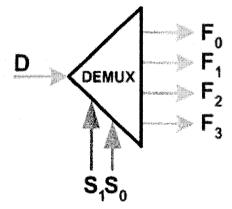

# 2.9 DEMULTIPLEXERS

They are digital switches which connect data from one input source to one of n outputs. Usually implemented by using n-to-2n binary decoders where the decoder enable line is used for data input of the de-multiplexer.

The figure below shows a de-multiplexer block diagram which has got s-bits-wide select input, one bbits-wide data input and n b-bits-wide outputs.

Example: 1-to-4 De-multiplexer

Truth table

| <b>S1</b> | <b>S</b> 0 | FO | F1 | F2 | F3 |

|-----------|------------|----|----|----|----|

| 0         | 0          | D  | 0  | 0  | 0  |

| 0         | 1          | 0  | D  | 0  | 0  |

| 1         | 0          | 0  | 0  | D  | 0  |

| 1         | 1          | 0  | 0  | 0  | D  |

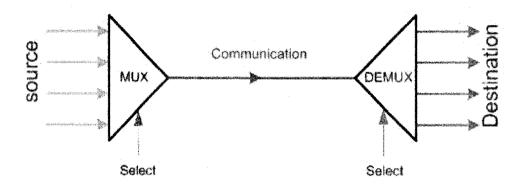

# Mux- Demux: Application Example

This enables sharing a single communication line among a number of devices. At any time, only one source and one destination can use the communication line.

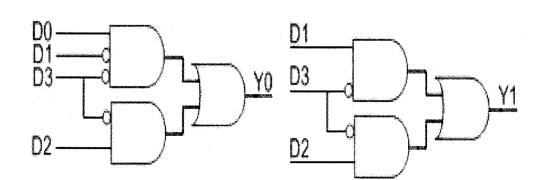

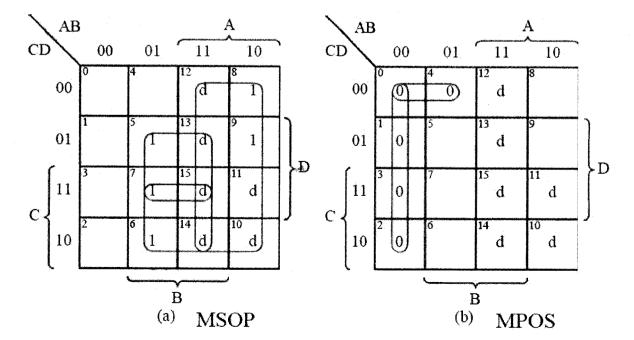

Example: Design a circuit to distinguish BCD digits  $\geq$  5 from those < 5.

| A<br>B<br>C<br>D | Logic   |                                                        |

|------------------|---------|--------------------------------------------------------|

| ABCD             | Minterm | <b>f</b> ( <b>A</b> , <b>B</b> , <b>C</b> , <b>D</b> ) |

| 0000             | 0       | 0                                                      |

| 0001             | 1       | 0                                                      |

| 0010             | 2       | 0                                                      |

| 0011             | 3       | 0                                                      |

| 0100             | 4       | 0                                                      |

| 0101             | 5       | 1                                                      |

| 0110             | 6       | 1                                                      |

| 0111             | 7       | 1                                                      |

| 1000             | 8       | 1                                                      |

| 1001             | 9       | 1                                                      |

| 1010             | 10      | d                                                      |

| 1011             | 11      | d                                                      |

| 1100             | 12      | d                                                      |

| 1101             | 13      | d                                                      |

| 1110             | 14      | d                                                      |

| 1111             | 15      | d                                                      |

# f(A,B,C,D) = A + BD + BC;

# f(A,B,C,D) = (A+B)(A+C+D)

# UNIT III

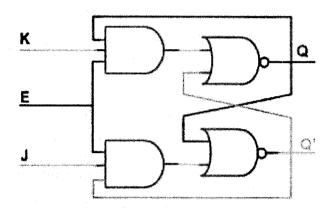

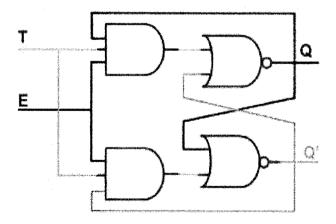

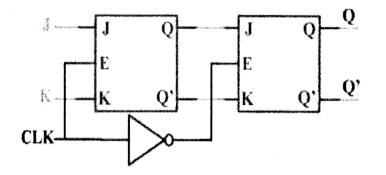

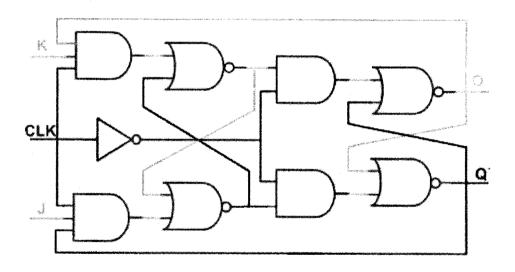

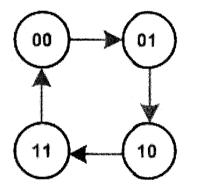

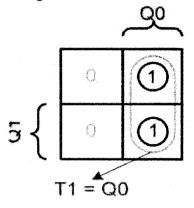

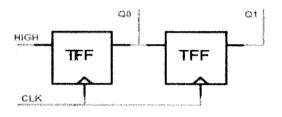

Flipflops Introduction – NAND LATCH, J K flipflop – J K Master – slave flipflop – D flipflop and T flipflop – Registers and Counters: Shift registers – serial in – parallelout, serial in – serial out, parallel in – serial out, parallel in – parallel out shift registers – wave forms for the above – Counters – up counters, down counters, decade counters, timing sequences, Mod – n counters.

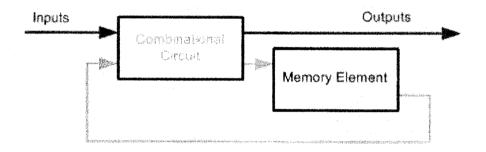

Digital electronics is classified into combinational logic and sequential logic. Combinational logic output depends on the inputs levels, whereas sequential logic output depends on stored levels and also the present inputs.

The memory elements are devices capable of storing binary info. The binary info stored in the memory elements at any given time defines the state of the sequential circuit. The input and the present state of the memory element determine the output. Memory elements next state is also a function of external inputs and present state. A sequential circuit is specified by a time sequence of inputs, outputs, and internal states.

There are two types of sequential circuits. Their classification depends on the timing of their signals:

- Synchronous sequential circuits

- Asynchronous sequential circuits

#### ✓ ASYNCHRONOUS SEQUENTIAL CIRCUIT

This is a system whose outputs depend upon the order in which its input variables change and can be affected at any instant of time. Gate-type asynchronous systems are basically combinational circuits with feedback paths. Because of the feedback among logic gates, the system may, at times, become unstable. Consequently they are not often used.

#### ✓ SYNCHRONOUS SEQUENTIAL CIRCUITS

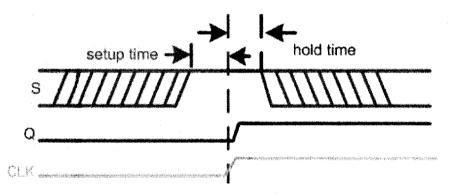

This type of system uses storage elements called flip-flops that are employed to change their binary value only at discrete instants of time. Synchronous sequential circuits use logic gates and flip-flop storage devices. Sequential circuits have a clock signal as one of their inputs. All state transitions in such circuits occur only when the clock value is either 0 or 1 or happen at the rising or falling edges of the clock depending on the type of memory elements used in the circuit. Synchronization is achieved by a timing device called a clock pulse generator. Clock pulses are distributed throughout the system in such a way that the flip-flops are affected only with the arrival of the synchronization pulse. Synchronous sequential circuits that use clock pulses in the inputs are called clocked-sequential circuits. They are stable and their timing can easily be broken down into independent discrete steps, each of which is considered separately.

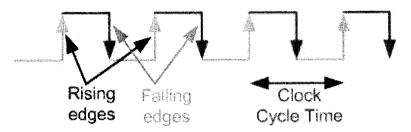

A clock signal is a periodic square wave that indefinitely switches from 0 to 1 and from 1 to 0 at fixed intervals. Clock cycle time or clock period: the time interval between two consecutive rising or

falling edges of the clock.

Clock Frequency = 1 / clock cycle time (measured in cycles per second or Hz)

# Example: Clock cycle time = 10ns clock frequency = 100M 3.1 CONCEPT OF SEQUENTIAL LOGIC

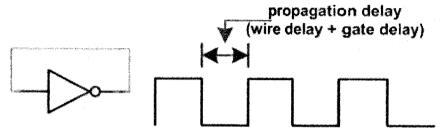

A sequential circuit is a combinational logic with some feedback to maintain its current value, like a memory cell. To understand the basics let's consider the basic feedback logic circuit below, which is a simple NOT gate whose output is connected to its input. The effect is that output oscillates between HIGH and LOW (i.e. 1 and 0). Oscillation frequency depends on gate delay and wire delay. Assuming a wire delay of 0 and a gate delay of 10ns, then oscillation frequency would be (on time + off time = 20ns) 50Mhz.

The basic idea of having the feedback is to store the value or hold the value, but in the above circuit, output keeps toggling. We can overcome this problem with the circuit below, which is basically cascading two inverters, so that the feedback is in-phase, thus avoids toggling. The equivalent circuit is the same as having a buffer with its output connected to its input.

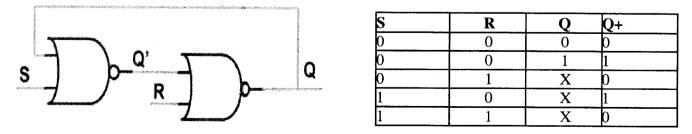

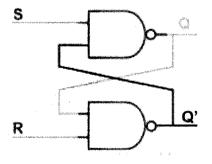

The circuit below is the same as the inverters connected back to back with provision to set the state of each gate (NOR is gate with both inputs shorted like a inverter). I am not going to explain the operation, as it is clear from the truthtable. S is called set and R is called **Reset**.

There still seems to be some problem with the above configuration, we cannot control when the input should be sampled, in other words here is no enable signal to control when the input is sampled.

Normally input enable signals can be of two types.

✓ Level Sensitive or (LATCH)

✓ Edge Sensitive œ (Flip-Flop)

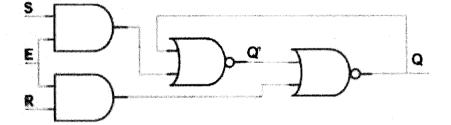

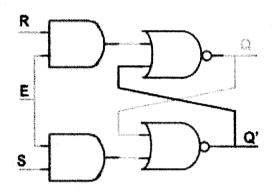

✓ Level Sensitive: The circuit below is a modification of the above one to have level sensitive enable input. Enable, when LOW, masks the input S and R. When HIGH, presents S and R to the sequential logic input (the above circuit two NOR Gates). Thus Enable, when HIGH, transfers input S and R to the sequential cell transparently, so this kind of sequential circuits are called transparent Latch. The memory element we get is an RS Latch with active high Enable.

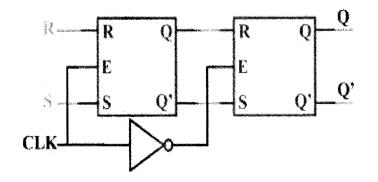

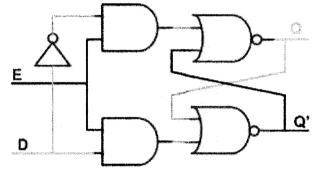

✓ Edge Sensitive: The circuit below is a cascade of two level sensitive memory elements, with a phase shift in the enable input between first memory element and second memory element. The first RS latch (i.e. the first memory element) will be enabled when CLK input is HIGH and the second RS batch will be enabled when CLK is LOW. The net effect is input RS is moved to Q and

Q' when CLK changes state from HIGH to LOW, this HIGH to LOW transition is called falling edge. So the Edge Sensitive element we get is called negative edge RS flip-flop.

# 3.2 LATCHES AND FLIP-FLOPS

There are two types of sequential circuits.

- Asynchronous Circuits.

- Synchronous Circuits.

Latches and Flip-flops are one and the same with a slight variation: Latches have level sensitive control signal input and Flip-flops have edge sensitive control signal input. Flip-flops and latches which use this control signals are called synchronous circuits. So if they don't use clock inputs, then they are called asynchronous circuits.

## ✓ RS Latch

RS latch have two inputs, S and R. S is called set and R is called reset. The S input is used to produce

HIGH on Q (i.e. store binary 1 in flip-flop). The R input is used to produce LOW on Q (i.e. store binary 0 in flip-flop). Q' is Q complementary output, so it always holds the opposite value of Q. The output of the S-R latch depends on current as well as previous inputs or state, and its state (value stored) can change as soon as its inputs change. The circuit and the truth table of RS latch is shown below.

| 5 | R | Q | Q+ |

|---|---|---|----|

| ) | 0 | 0 | 0  |

| ) | 0 | 1 | 1  |

| ) | 1 | Х | 0  |

| 1 | 0 | X | 1  |

| 1 | 1 | Х | 0  |

The operation has to be analyzed with the 4 inputs combinations together with the 2 possible previous states.

• When S = 0 and R = 0: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 0 and Q' = (S + Q)'

= 1. So it is clear that when both S and R inputs are LOW, the output is retained as before the application of inputs. (i.e. there is no state change).

• When S = 1 and R = 0: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 1 and Q' = (S + Q)'

= 0. So in simple words when S is HIGH and R is LOW, output Q is HIGH.

• When S = 0 and R = 1: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 0 and Q' = (S + Q)' = 1. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 0 and Q' = (S + Q)'

= 1. So in simple words when S is LOW and R is HIGH, output Q is LOW.

When S = 1 and R =1: No matter what state Q and Q' are in, application of 1 at input of NOR gate always results in 0 at output of NOR gate, which results in both Q and Q' set to LOW (i.e. Q = Q'). LOW in both the outputs basically is wrong, so this case is invalid.

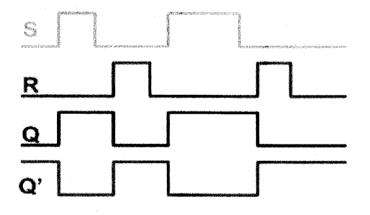

The waveform below shows the operation of NOR gates based RSLatch.

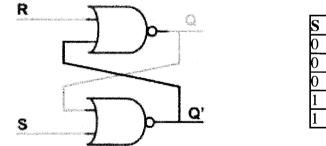

It is possible to construct the RS latch using NAND gates. The circuit and Truth table of RS latch using NAND is shown below.

| S | R | Q | Q+ |  |

|---|---|---|----|--|

| 1 | 1 | 0 | 0  |  |

| 1 | 1 | 1 | 1  |  |

| 0 | 1 | X | 0  |  |

| 1 | 0 | X | 1  |  |

| 0 | 0 | X | 1  |  |

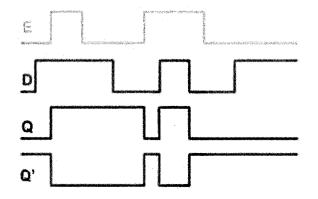

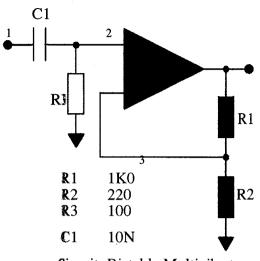

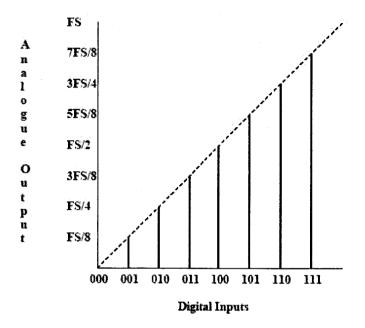

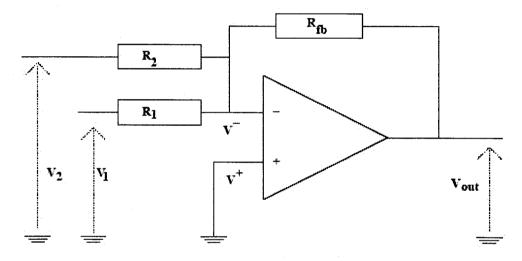

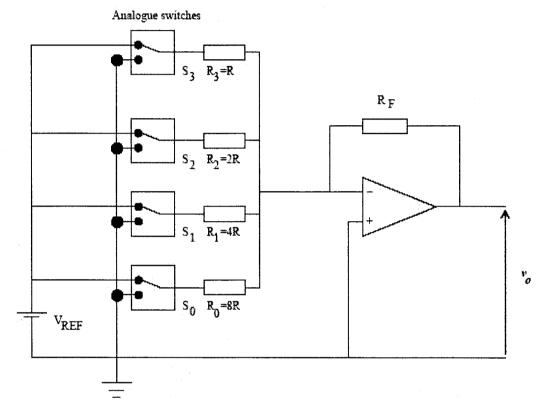

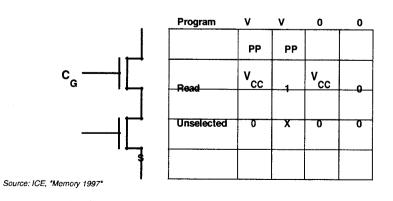

#### **RS Latch** with Clock